**Course Code:- CSM-6112**

**Course Name:- Computer**

**Organization &**

**Architecture**

# **MASTER OF COMPUTER APPLICATIONS (MCA)**

## **PROGRAMME DESIGN COMMITTEE**

|                                                                     |                                                                                                         |                                                                        |

|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Prof. Masood Parvez<br>Vice Chancellor – Chairman<br>MTSOU, Tripura | Prof. C.R.K. Murty<br>Professor of Distance Education<br>IGNOU, New Delhi                               | Prof. P.V. Suresh<br>Professor of Computer Science<br>IGNOU, New Delhi |

| Prof. Abdul Wadood Siddiqui<br>Dean Academics<br>MTSOU, Tripura     | Prof. Mohd. Nafees Ahmad Ansari<br>Director of Distance Education<br>Aligarh Muslim University, Aligarh | Prof. V.V. Subrahmanyam<br>Professor of Computer Science               |

## **COURSE WRITER**

|                                                                                                                                            |                                                                                                                                        |                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Dr. Md. Amir Khusru Akhtar<br>Associate Professor of Computer Science<br>MTSOU, Tripura<br>CSM-6111 Data Communication & Computer Networks | Dr. Manish Saxena<br>Assistant Professor of Computer Science<br>MTSOU, Tripura<br>CSM-6113 Discrete Mathematics                        | Mr. Pankaj Kumar<br>Assistant Professor of Computer Science<br>Mangalayatan University, Aligarh<br>CSM-6151 Programming with 'C' & Lab |

| Dr. Ankur Kumar<br>Assistant Professor<br>MTSOU, Tripura<br>CSM-6112 Computer Organization & Architecture                                  | Dr. Duvvuri B. K. Kamesh<br>Assistant Professor of Computer Science<br>MTSOU, Tripura<br>CSM-6114 Accountancy and Financial Management | Ms. Vanshika Singh<br>Assistant Professor of English<br>MTSOU, Tripura<br>ENM-6101 Professional Communication                          |

## **COURSE EDITORS**

|                                                                                                     |                                                                                 |                                                                                 |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Prof. S. Nagakishore Bhavanam<br>Professor of Computer Science<br>Mangalayatan University, Jabalpur | Dr. Manoj Varshney<br>Associate Professor of Computer Science<br>MTSOU, Tripura | Associate Professor of Computer Science<br>IGNOU, New Delhi                     |

| Prof. Jawed Wasim<br>Professor of Computer Science<br>Mangalayatan University, Aligarh              | Dr. M. P. Mishra                                                                | Dr. Akshay Kumar<br>Associate Professor of Computer Science<br>IGNOU, New Delhi |

## **FORMAT EDITORS**

|                                                                        |                                                  |                                                                        |

|------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------|

| Dr. Nitendra Singh<br>Associate Professor of English<br>MTSOU, Tripura | Assistant Professor of English<br>MTSOU, Tripura | MTSOU, Tripura                                                         |

| Ms. Angela Fatima Mirza                                                | Dr. Faizan<br>Assistant Professor of English     | Ms. Vanshika Singh<br>Assistant Professor of English<br>MTSOU, Tripura |

## **MATERIAL PRODUCTION**

1. Mr. Himanshu Saxena

2. Ms. Rainu Verma

3. Mr. Jeetendra Kumar

4. Mr. Khiresh Sharma

5. Mr. Ankur Kumar Sharma

6. Mr. Pankaj Kumar

# CONTENT

|                                                                                                                                                                                                                                                                                                                      | <b>Page No.</b> |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| <b>Block 1 ; Represetation of Information and Basic Building Blocks</b>                                                                                                                                                                                                                                              | <b>05-146</b>   |

| Unit 1: Introduction to Computer, Computer hardware generation, Number System: Binary, Octal, Hexadecimal, Character Codes (BCD, ASCII, EBCDIC).                                                                                                                                                                     |                 |

| Unit 2: Logic gates, Boolean Algebra, K-map simplification, Half Adder, Full Adder, Subtract or, Decoder, Encoders, Multiplexer, Demultiplexer.                                                                                                                                                                      |                 |

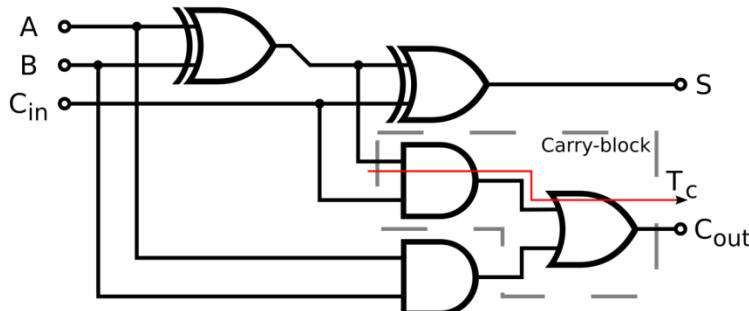

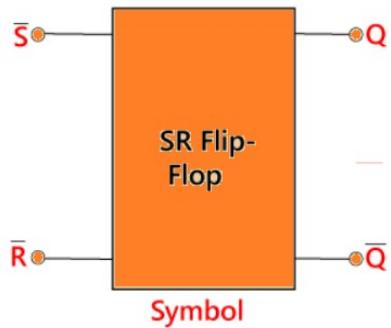

| Unit 3: Carry look ahead adder, Combinational logic Design, Flip-Flops, Registers, Counters (synchronous & asynchronous).                                                                                                                                                                                            |                 |

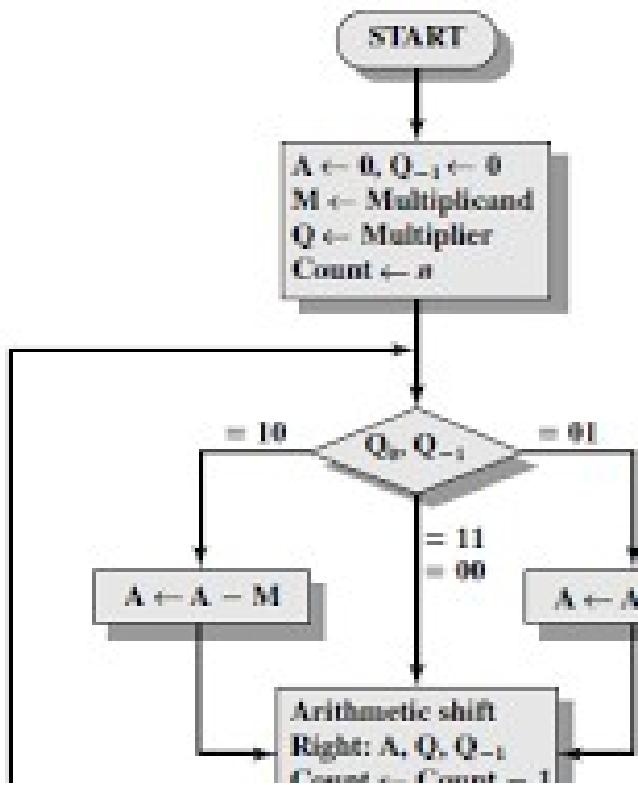

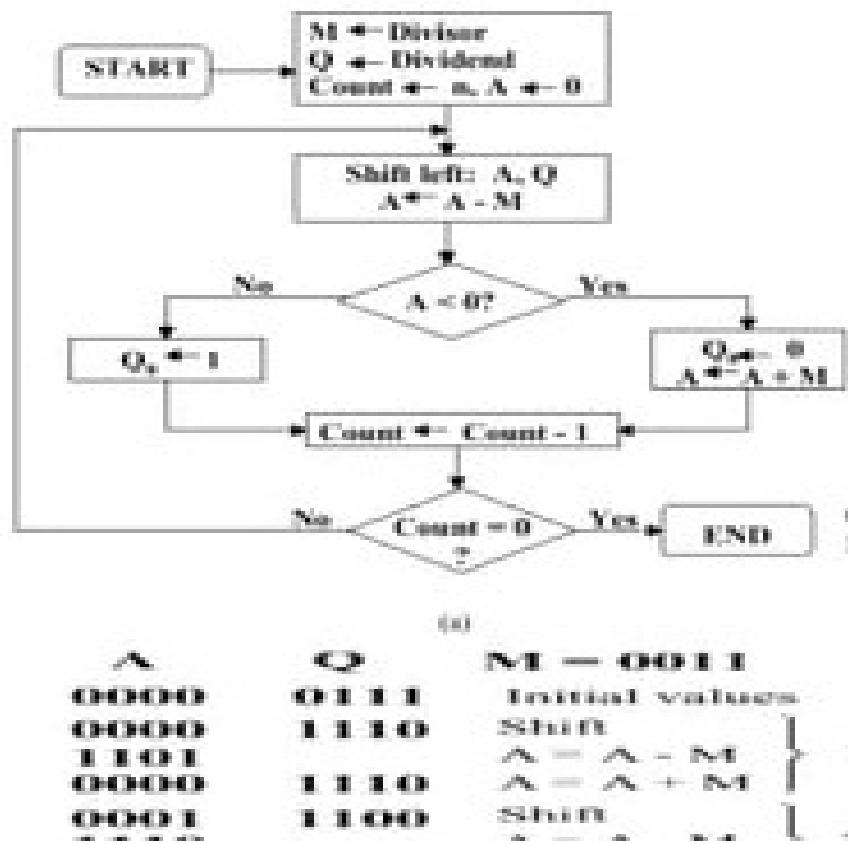

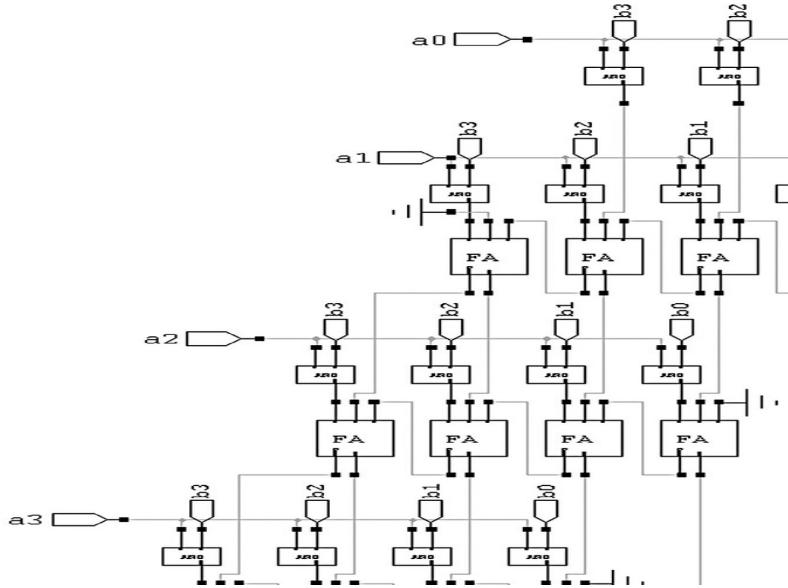

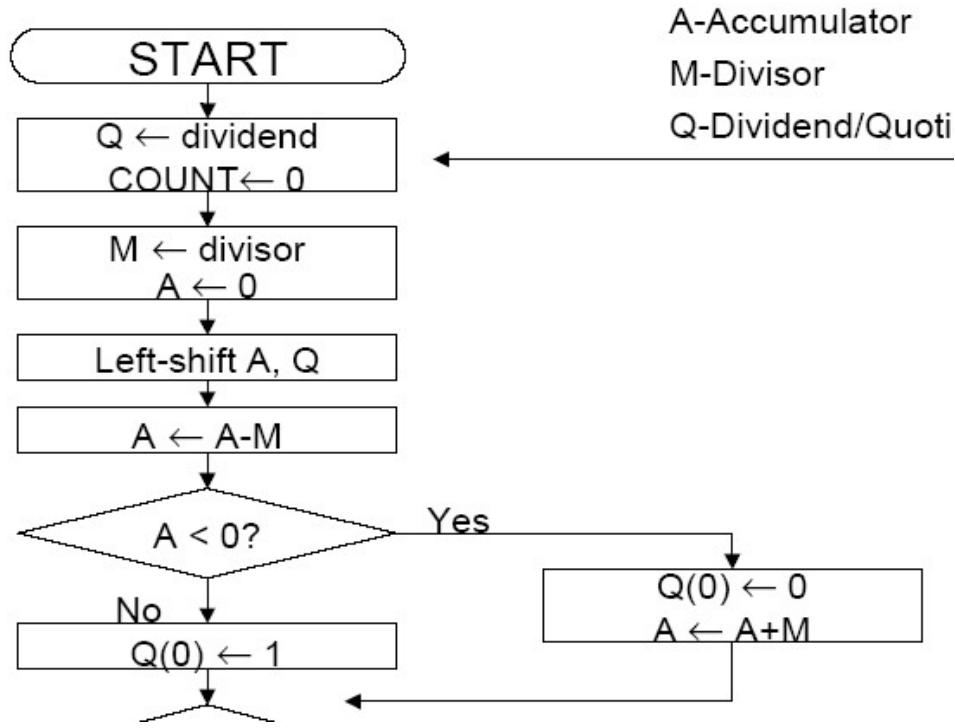

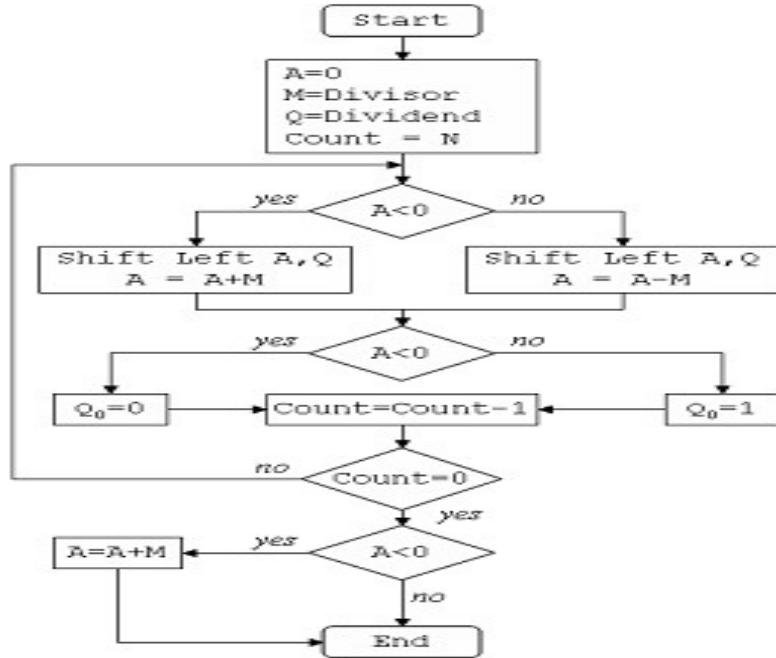

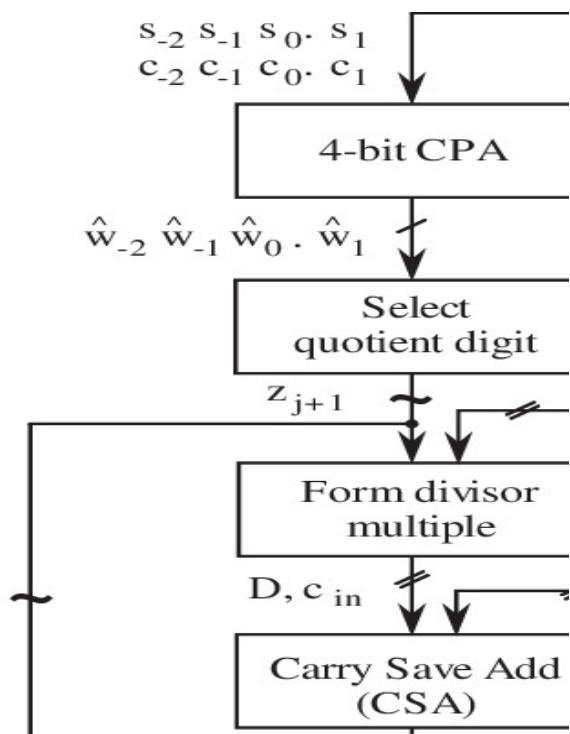

| Unit 4: ALU, Micro-Operation. ALU- chip, Faster Algorithm and Implementation (multiplication & Division).                                                                                                                                                                                                            |                 |

| <b>Block II: Basic Organization</b>                                                                                                                                                                                                                                                                                  | <b>147-243</b>  |

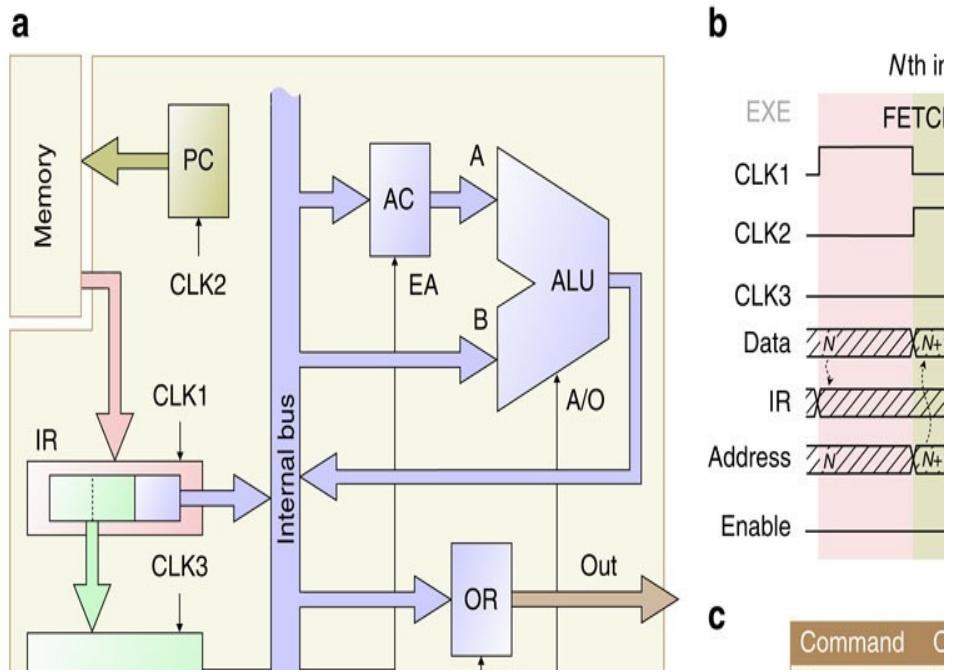

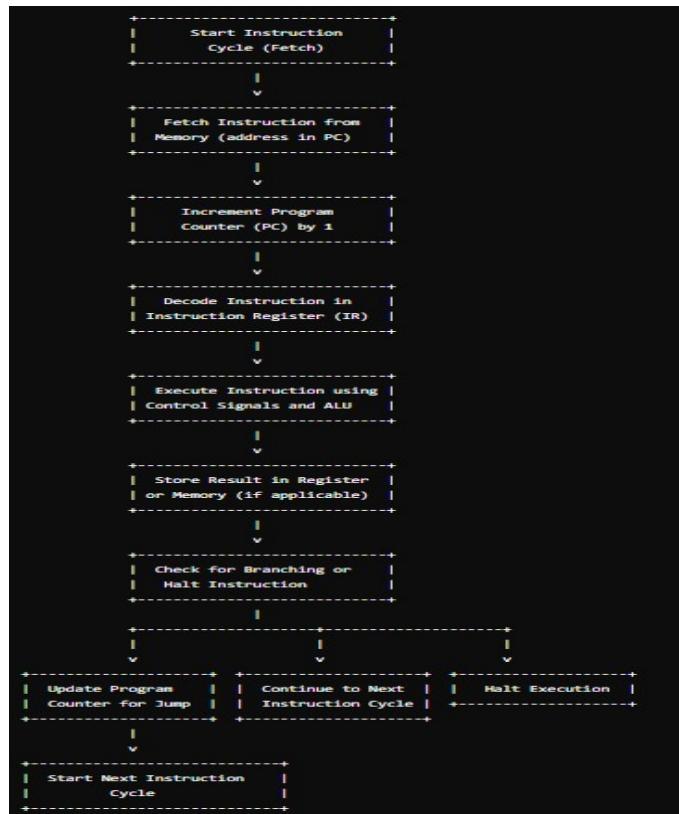

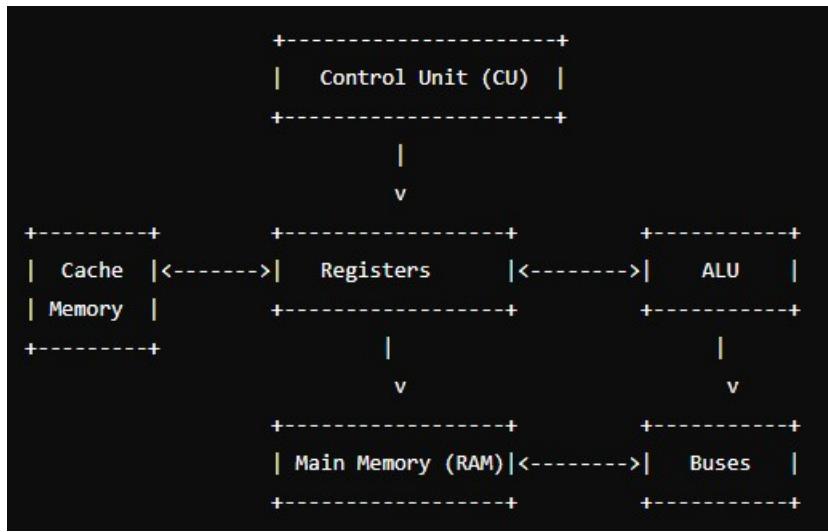

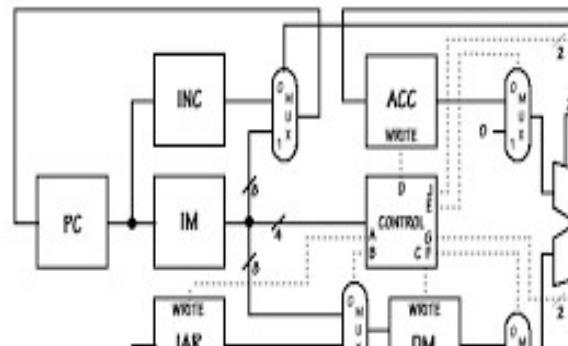

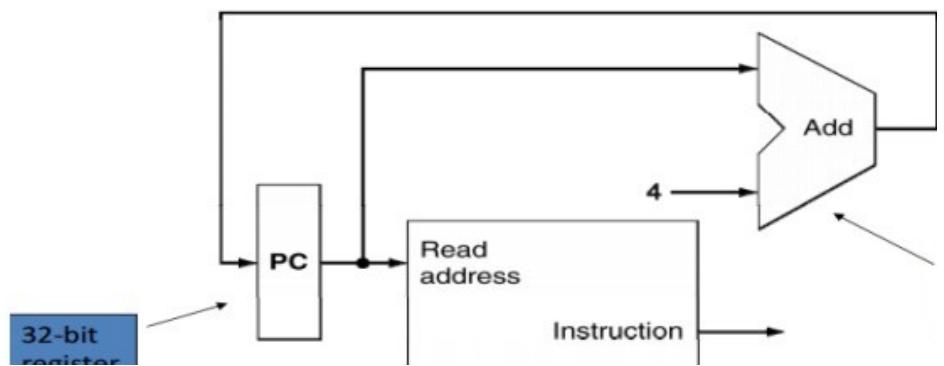

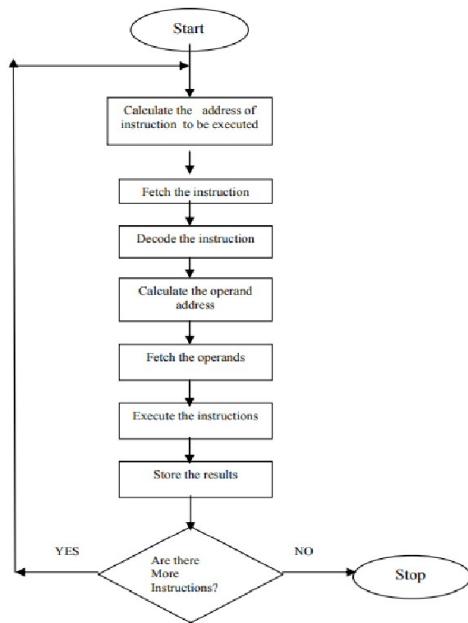

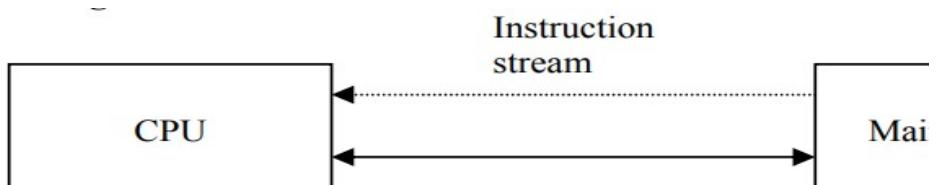

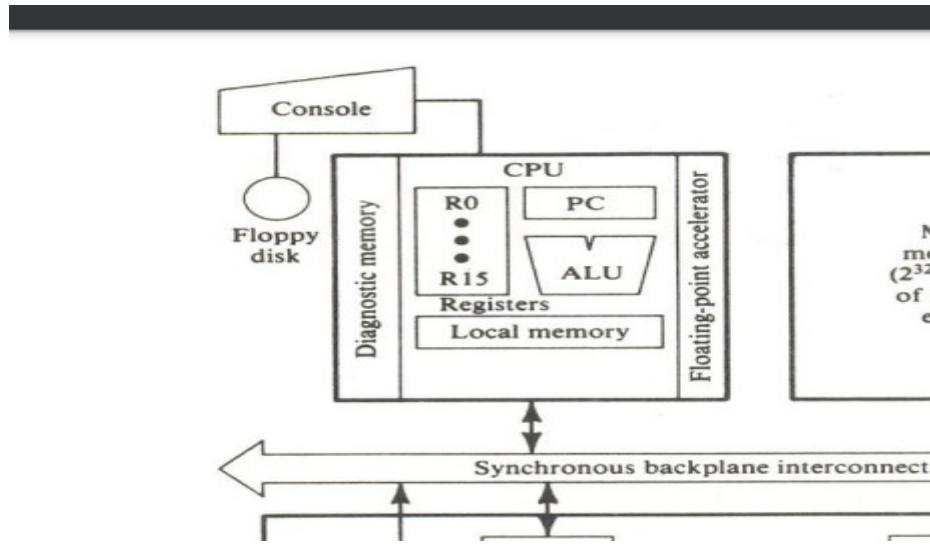

| Unit 5: Von Neumann Machine (IAS Computer), Operational flow chart (Fetch, Execute), Instruction Cycle, Organization of Central Processing Unit.                                                                                                                                                                     |                 |

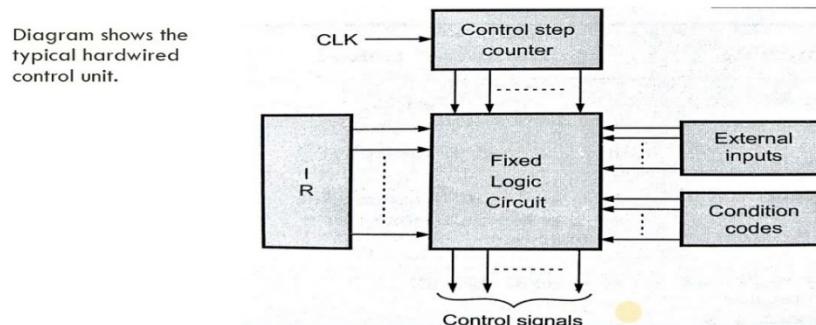

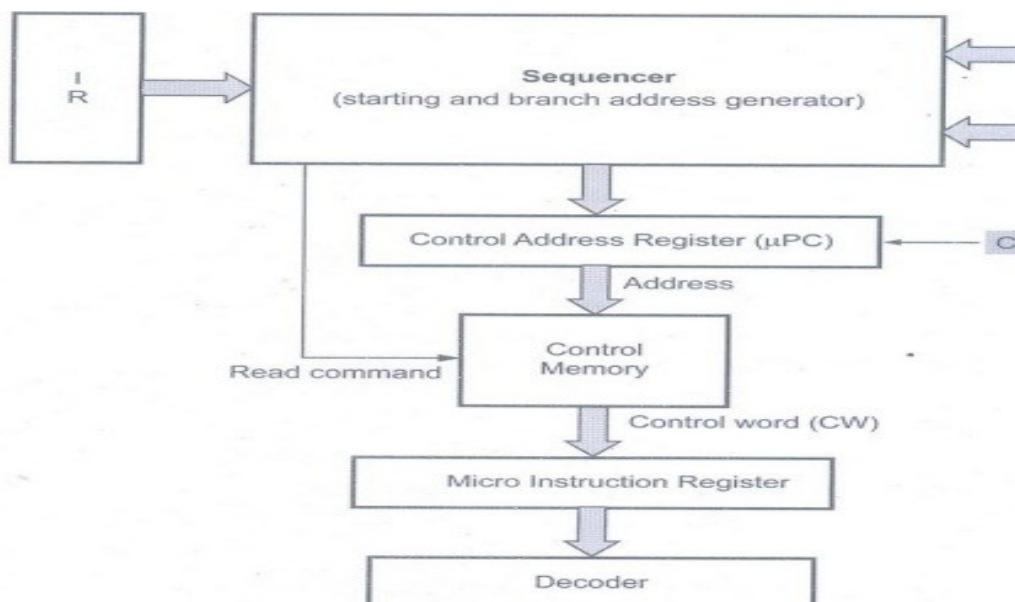

| Unit 6: Hardwired & micro programmed control unit, Single Organization, General Register Organization, Stack Organization.                                                                                                                                                                                           |                 |

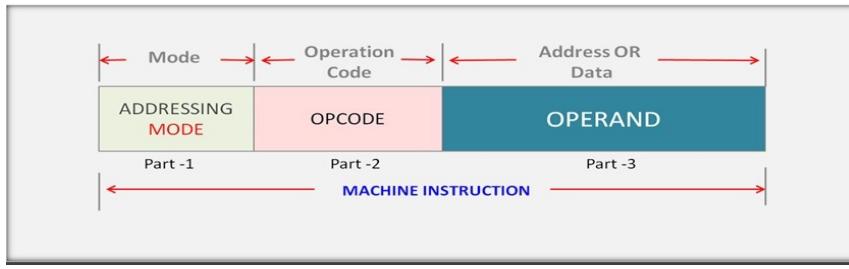

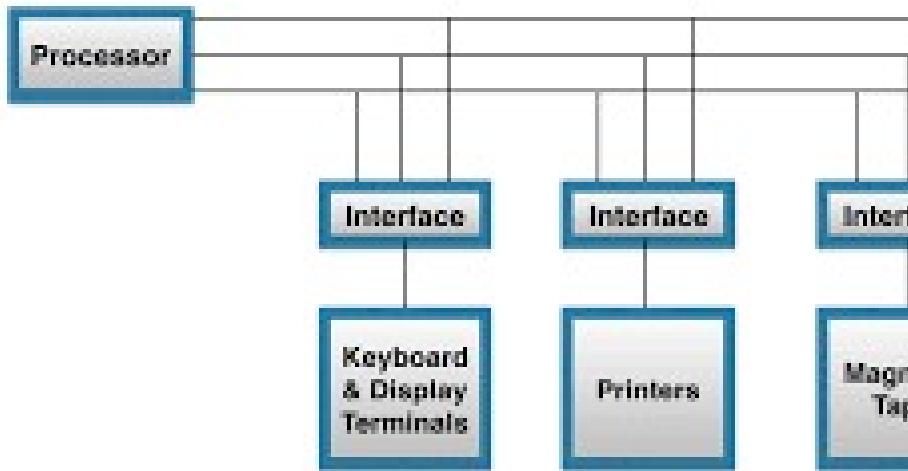

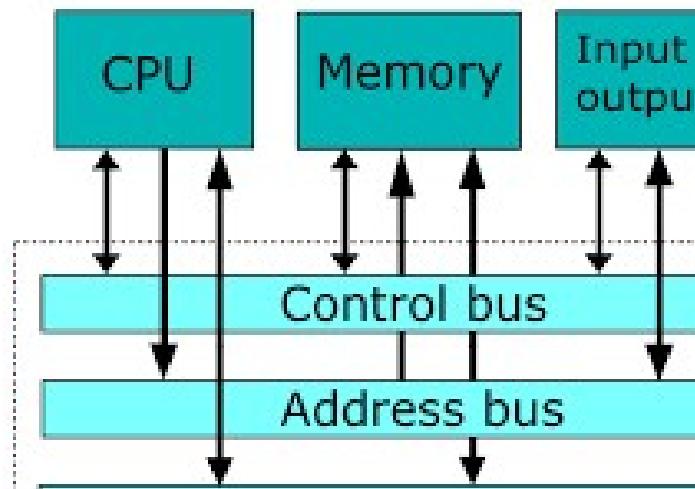

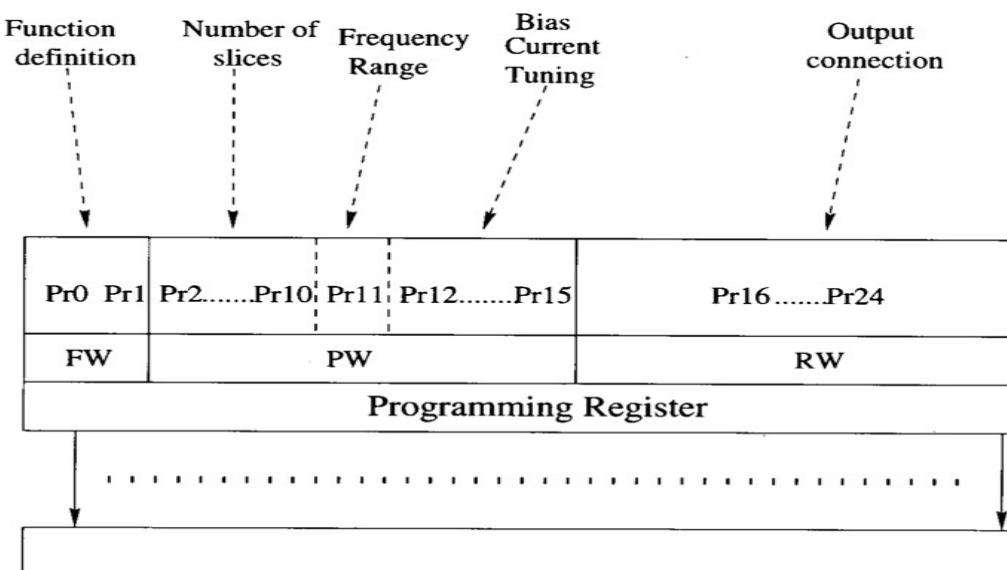

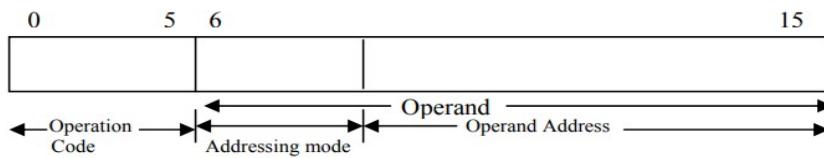

| Unit 7: Addressing modes, Instruction formats, data transfer & Manipulation, I/O Organization, Bus Architecture, Programming Registers.                                                                                                                                                                              |                 |

| <b>Block III: Memory Organization &amp; I/O Organization</b>                                                                                                                                                                                                                                                         | <b>244-370</b>  |

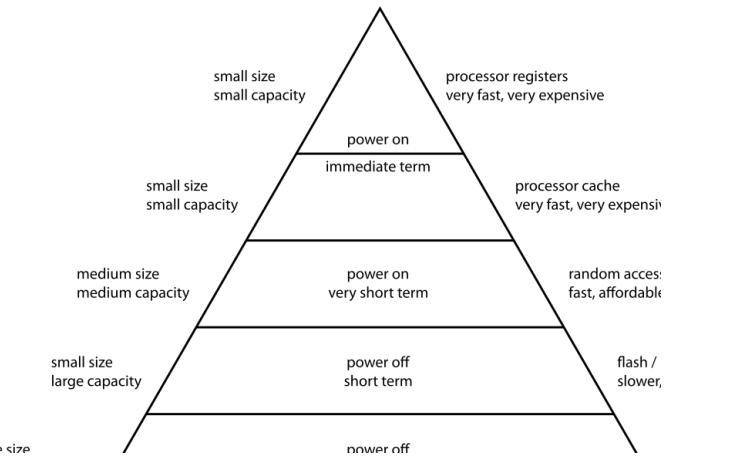

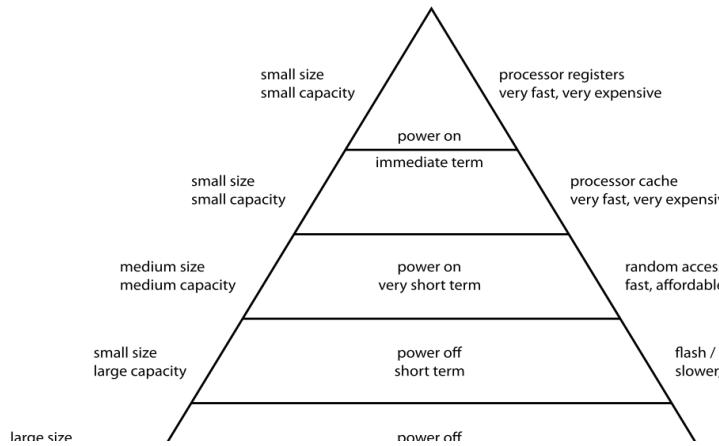

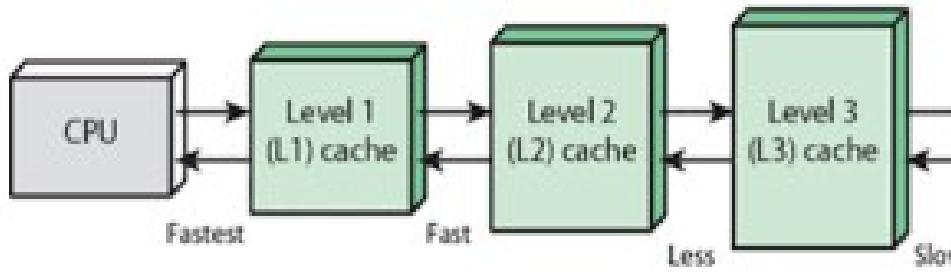

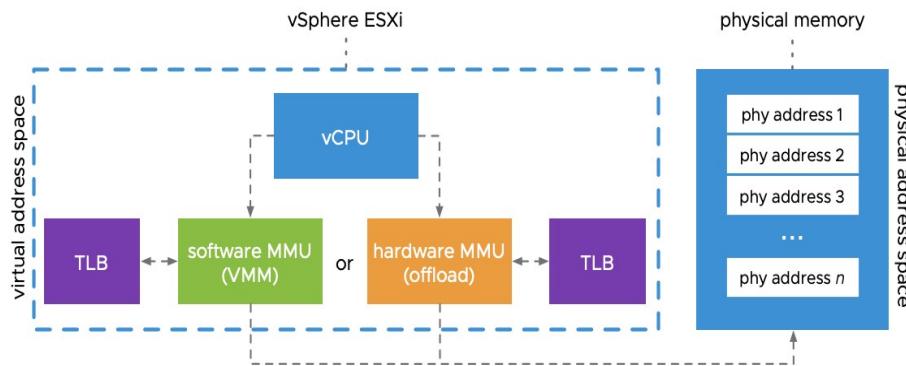

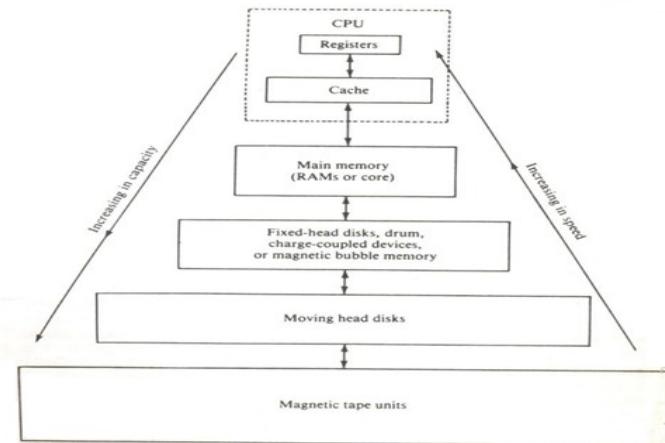

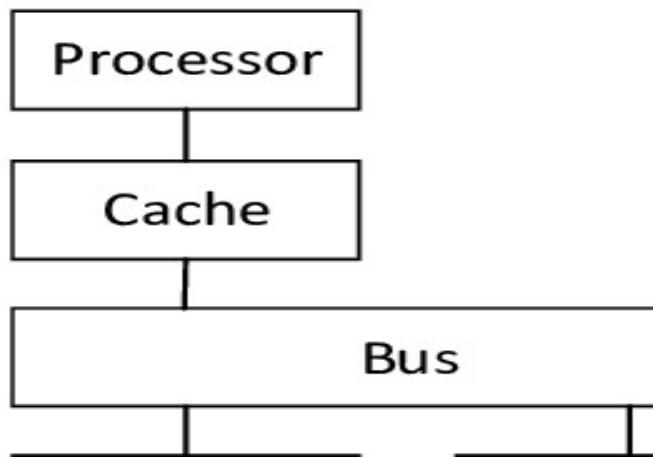

| Unit 8: Memory Hierarchy, Main memory (RAM/ROM chips), Auxiliary memory, Associative memory, Cache memory, Virtual Memory.                                                                                                                                                                                           |                 |

| Unit 9: Memory Management Hardware, hit/miss ratio, magnetic disk and its performance, magnetic Tape etc.                                                                                                                                                                                                            |                 |

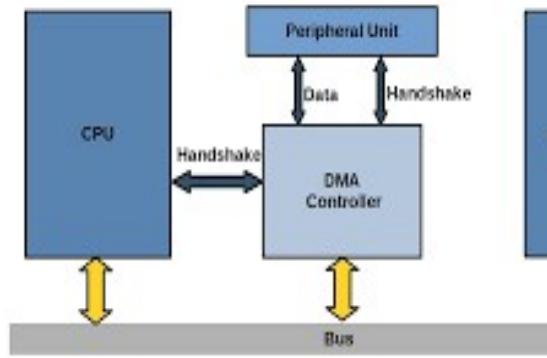

| Unit 10: Peripheral devices, I/O interface, Modes of Transfer, Priority Interrupt, Direct Memory Access, Input-Output Processor.                                                                                                                                                                                     |                 |

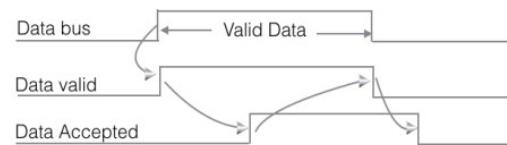

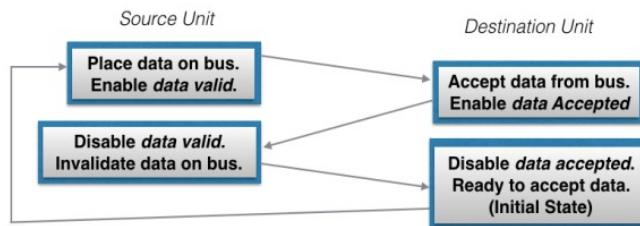

| Unit 11: Serial Communication. I/O Controllers, Asynchronous data transfer, Strobe Control, Handshaking.                                                                                                                                                                                                             |                 |

| <b>Block IV: Process Organization</b>                                                                                                                                                                                                                                                                                | <b>371-525</b>  |

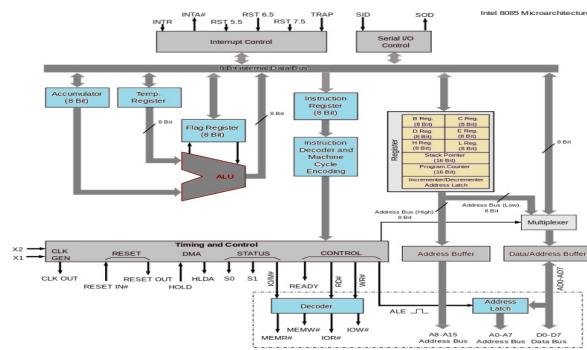

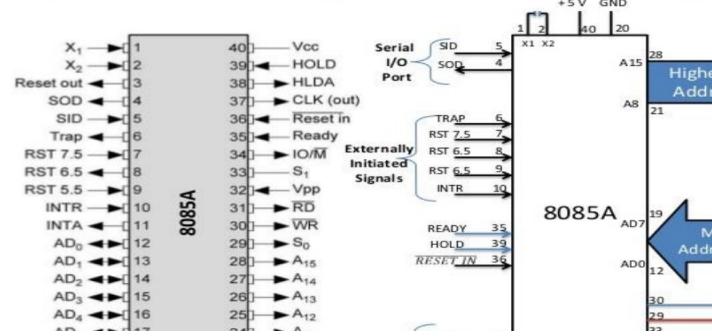

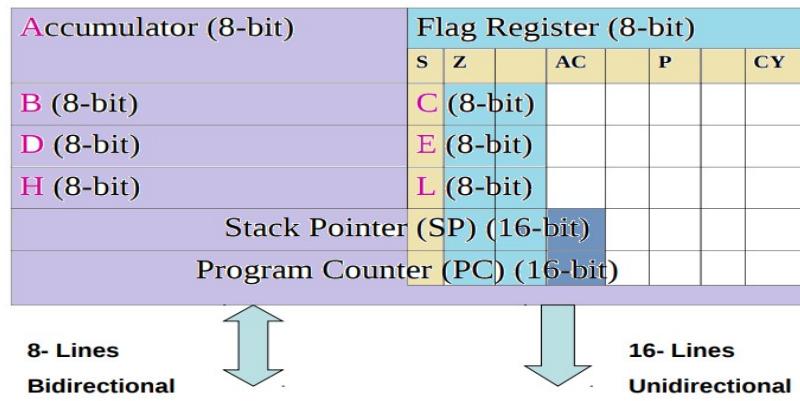

| Unit 12: Basic Concept of 8-bit micro Processor (8085) and 16-bit Micro Processor (8086), Assembly Instruction Set.                                                                                                                                                                                                  |                 |

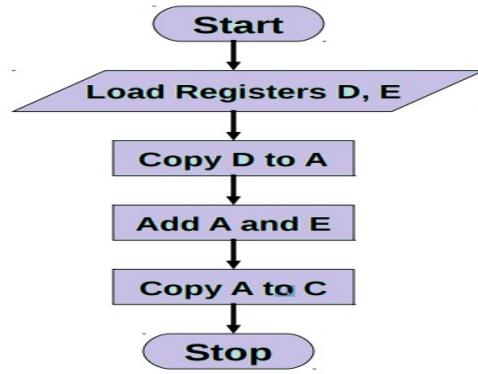

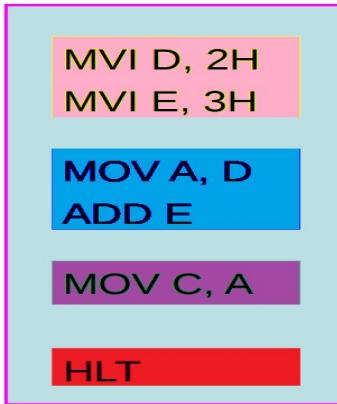

| Unit 13: Assembly language program of (8085): Addition of two numbers, Subtraction, Block Transfer, find greatest number.                                                                                                                                                                                            |                 |

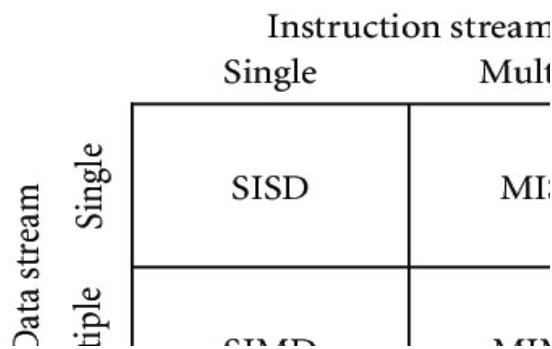

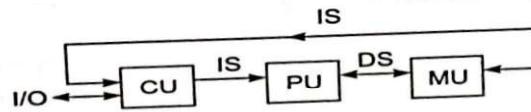

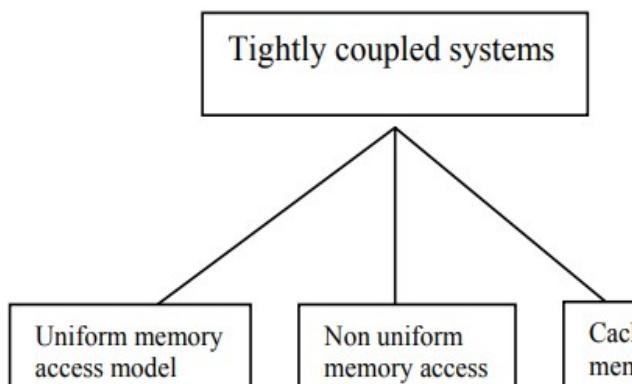

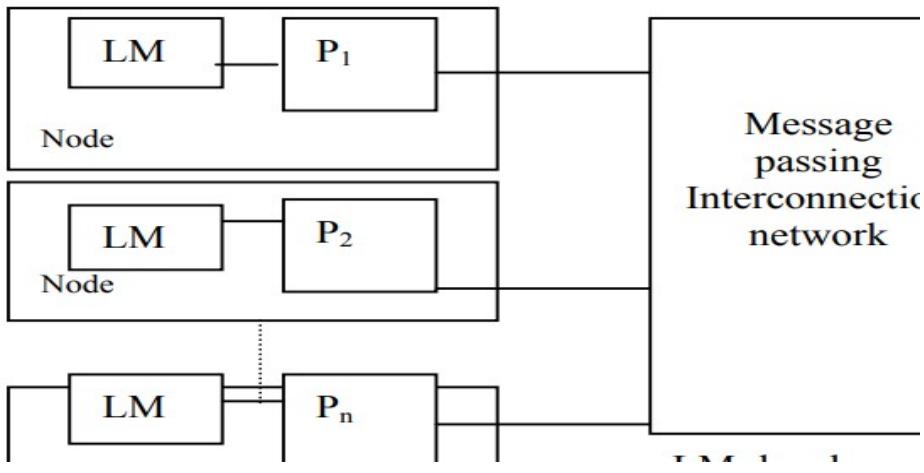

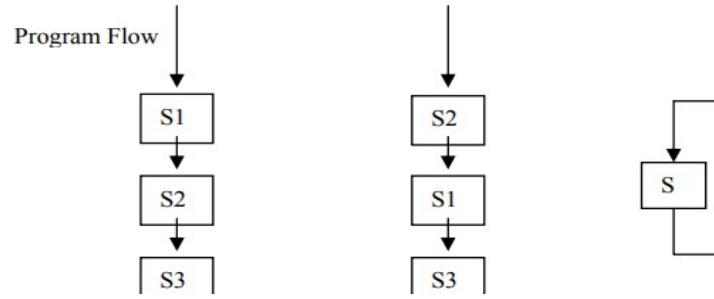

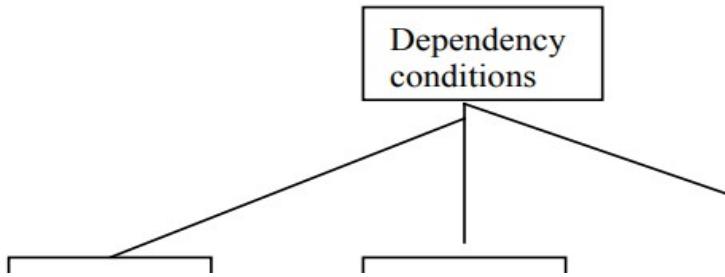

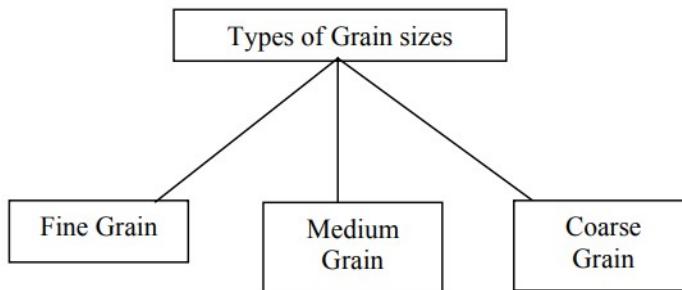

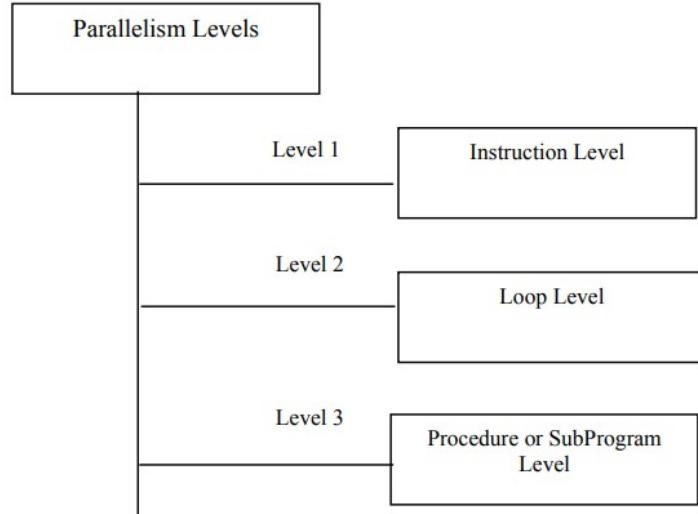

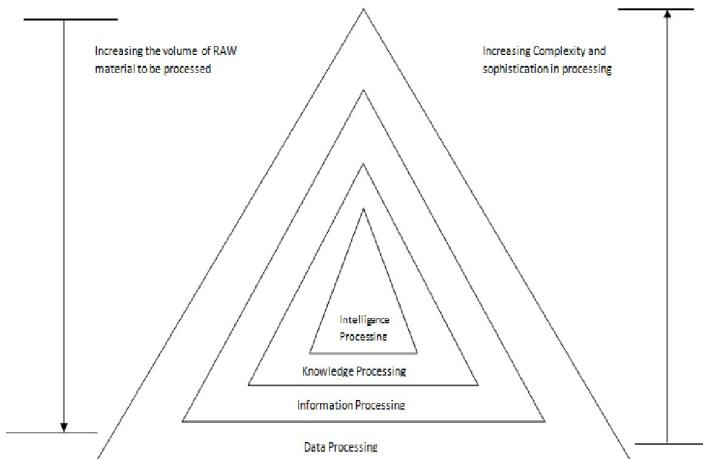

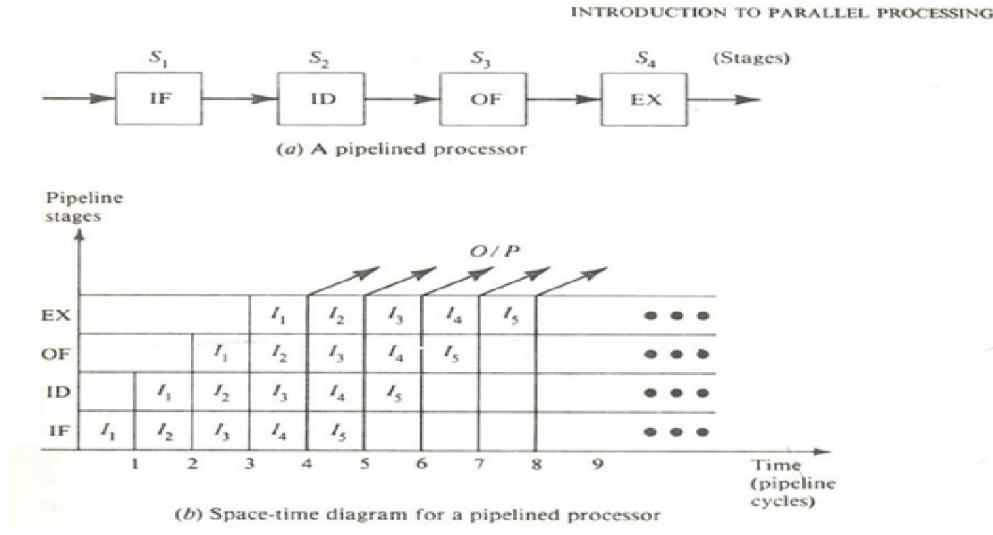

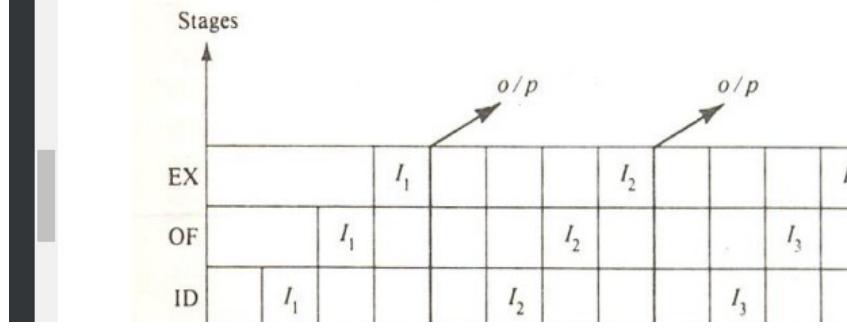

| Unit 14: Table search, Numeric Manipulation, Introductory Concept of pipeline, Flynn's and Feng's Classification, Parallel Architectural classification.                                                                                                                                                             |                 |

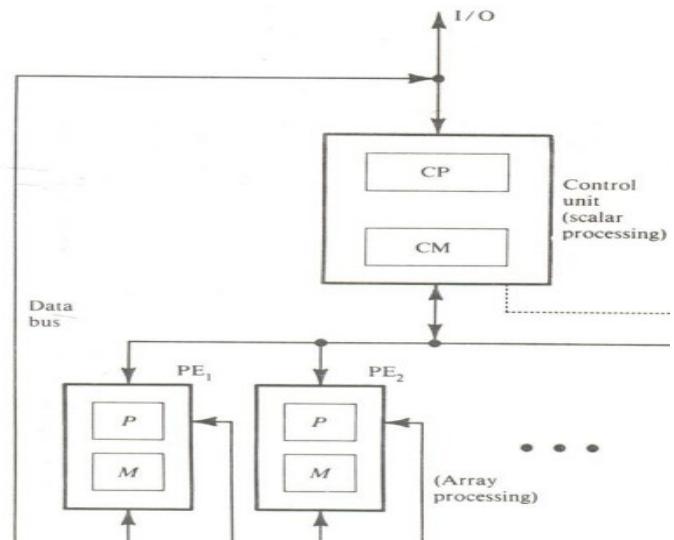

| Unit 15: Parallel Processing Concepts: Understanding parallel processing concepts including parallelism types (task-level, data-level, instruction-level) and parallel architectures (SIMD, MIMD), Multiprocessing Systems, Scalability and Load Balancing.                                                          |                 |

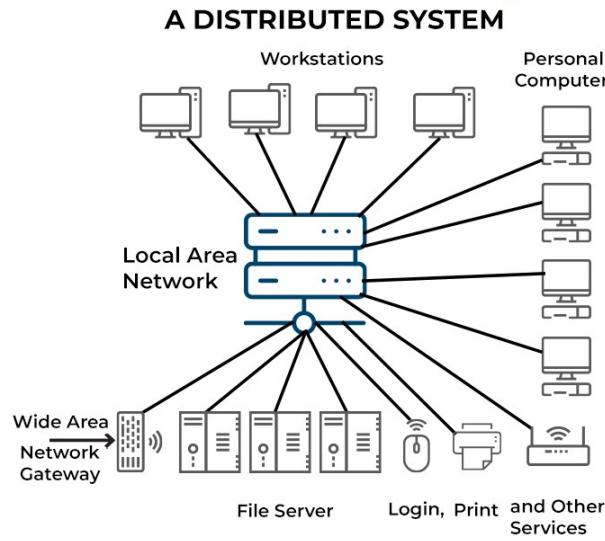

| Unit 16: System-Level Organization: System Architectures, Analyzing system architectures including single-processor systems, multiprocessor systems, and distributed systems. Scalability and Reliability: Evaluating system-level scalability and reliability considerations in large-scale computing environments. |                 |

# **BLOCK I: REPRESENTATION OF INFORMATION AND BASIC BUILDING BLOCKS**

## **UNIT – 1: BASICS OF COMPUTERS**

### **Structure**

- 1.0 Introduction

- 1.1 Objectives

- 1.2 Introduction to Computer

- 1.2.1 Computer Applications

- 1.3 Computer Generations

- 1.4 Number System

- 1.5 Conversion Techniques

- 1.6 Character Codes

- 1.7 Conclusion

- 1.8 Unit Based Questions & Answers

- 1.9 References

---

## **1.0 INTRODUCTION**

---

In today's digital age, computers have become an integral part of our daily lives. From simple calculations to complex simulations, computers have revolutionized the way we work, communicate, and entertain ourselves. Understanding the basics of computers and their underlying technology is essential for anyone seeking to navigate this digital landscape.

This unit aims to provide a comprehensive introduction to the fundamentals of computers, covering topics such as computer applications, generations, number systems, conversion techniques,

and character codes. By the end of this unit, students will have a solid understanding of the principles that underlie computer systems and be able to apply this knowledge in practical ways.

In this introduction, we will set the stage for the topics that will be covered in this unit. We will explore the various applications of computers, the different generations of computer technology, and the basic concepts of number systems and character codes. This foundation will provide a solid base for understanding the more advanced topics that will be covered in subsequent units.

---

## **1.1 OBJECTIVES**

---

By the end of this unit, students will be able to understand,

- Understand the basic components and applications of computers

- Identify and describe the different generations of computer technology

- Explain the concept of number systems and perform conversions between different number systems (binary, decimal, hexadecimal)

- Understand the importance of character codes and their uses

- Apply knowledge of computer fundamentals to real-world scenarios

- Analyze and solve problems related to computer systems and technology

- Develop critical thinking skills in understanding computer concepts and terminology

## **1.2 INTRODUCTION TO COMPUTER**

---

A computer is an electronic device that manipulates information or data. It has the ability to store, retrieve, and process data. Computers can be used to type documents, send emails, play games, and browse the Web. They are also used to handle spreadsheets, accounting, database management, presentations, and more.

### **Basic Functions of a Computer**

Computers perform four primary functions:

1. **Input:** The process of entering data and instructions into a computer system. Input devices include keyboards, mice, scanners, and microphones.

2. **Processing:** The manipulation of data by the computer's central processing unit (CPU) to convert data into information. This includes performing calculations, making decisions, and executing programs.

3. **Storage:** Saving data and instructions in the computer's memory for future use. There are two main types of storage:

- o **Primary Storage** (RAM - Random Access Memory): Temporary storage used while the computer is running.

- o **Secondary Storage** (HDD, SSD, USB drives): Permanent storage used to save data and programs.

4. **Output:** The process of displaying or producing information from the computer. Output devices include monitors, printers, speakers, and projectors.

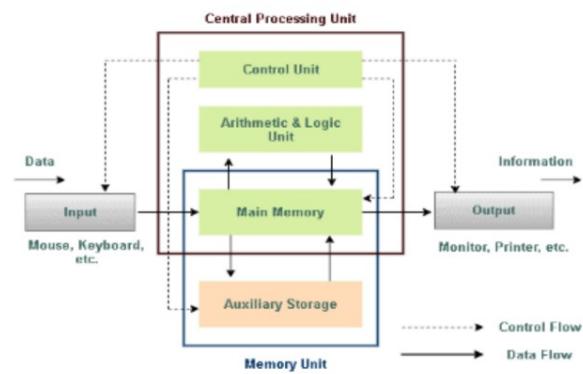

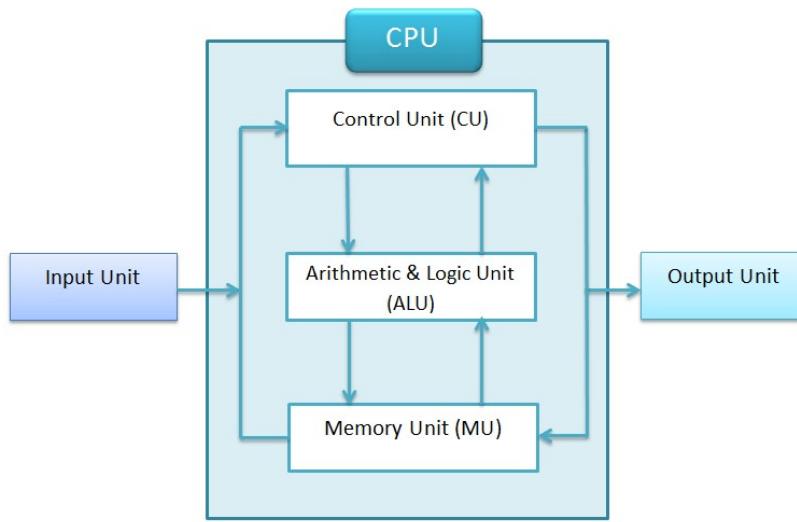

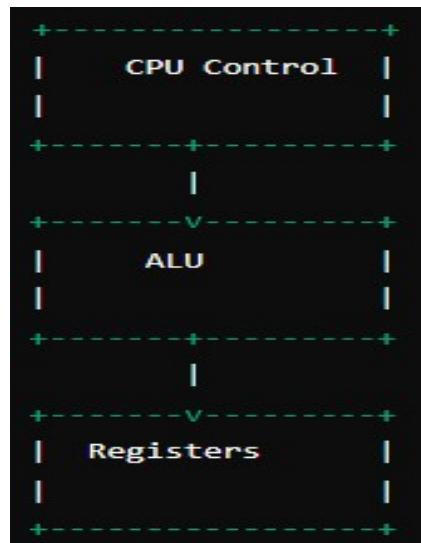

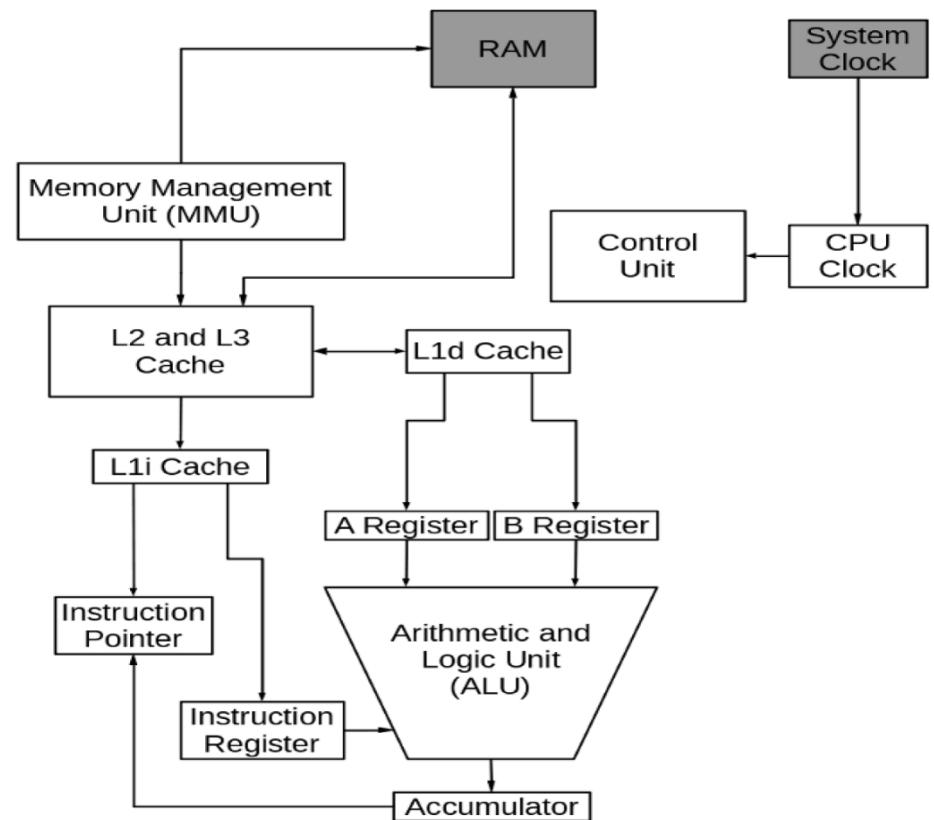

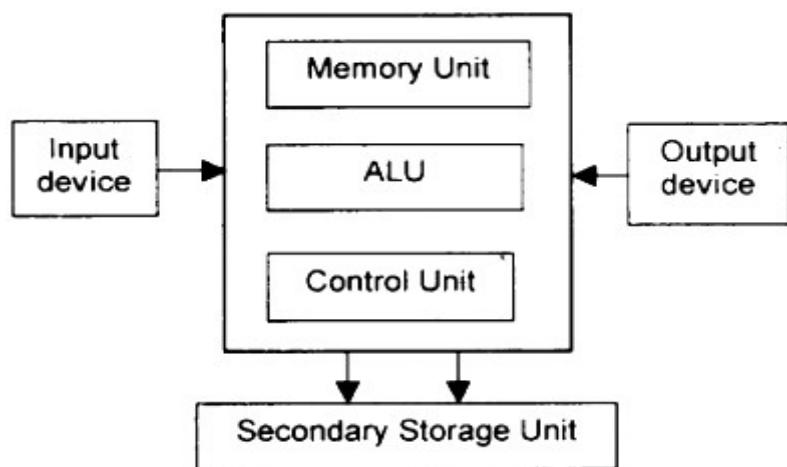

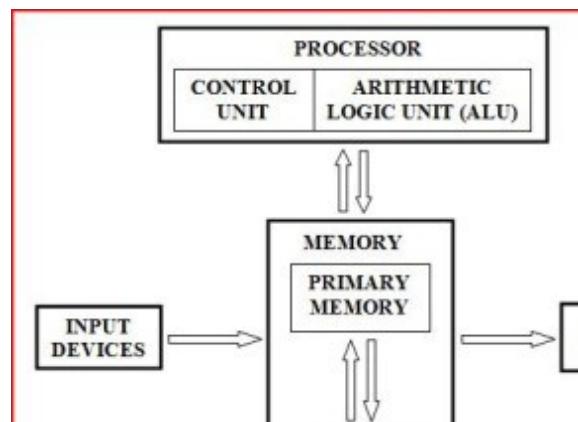

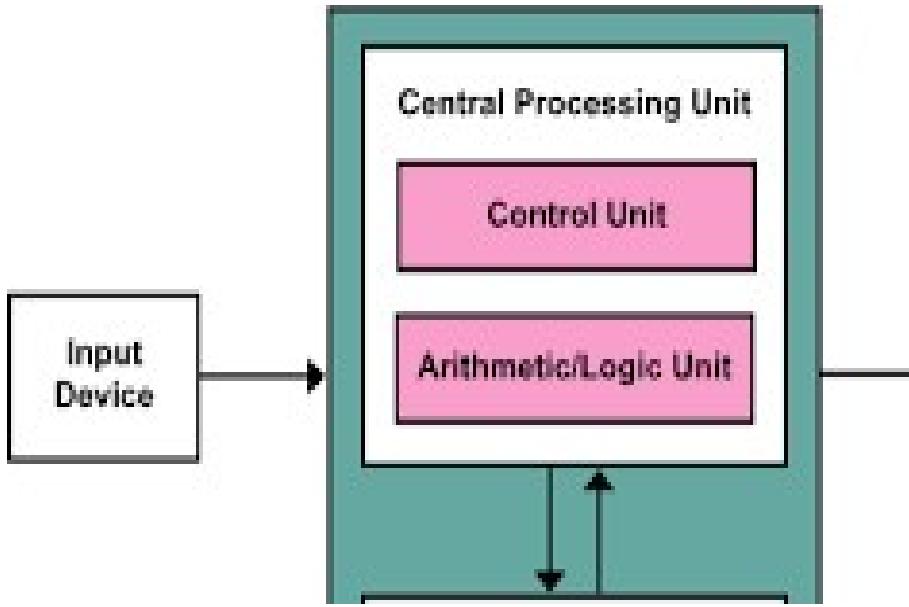

**The block diagram of a computer is composed of numerous important parts.**

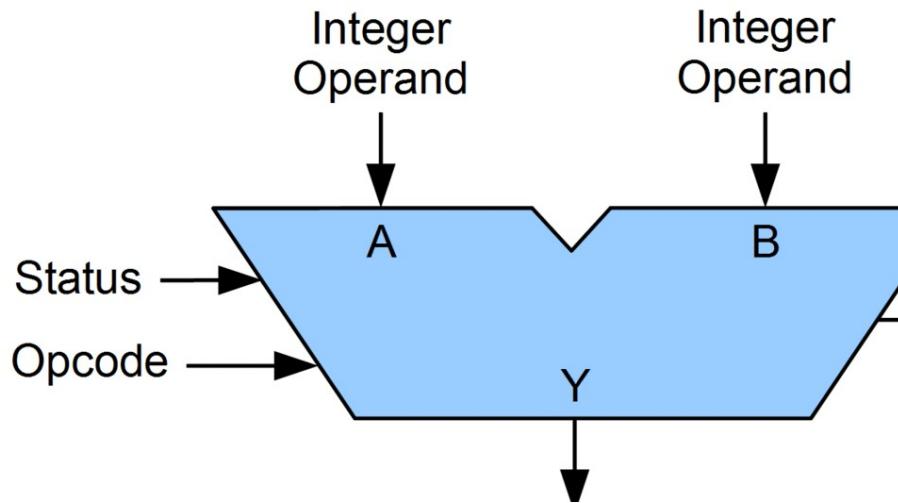

The Arithmetical and Logical Unit is in charge of using arithmetical and logical expressions to do calculations and make judgments.

- **Control Unit (CU):** This part of the computer system is responsible for monitoring and controlling the overall processes to make sure they are planned and executed properly.

- **Registers:** Integrated into the CPU, registers are little, fast memory modules. They are in charge of keeping track of the information and commands that the CPU is currently processing.

- **Memory Unit:** The memory unit functions as the computer system's storage component, holding data and program statements for both short- and long-term storage.

- **Input and Output Unit:** The input and output unit is in charge of transmitting and receiving data, enabling communication between the computer and external devices, and displaying information to the user, usually via a display.

## Types of Computers

A variety of computers are offered in different weights, sizes, and designs. They can do a variety of jobs because of their size and shape. They fit into a variety of categories. The computers are designed by qualified computer architects who fulfill certain specifications. Different sizes and forms are utilized by computers in households and hospitals. The many categories of computers will be discussed in the sections that follow. An advanced computer's capacity is based on how well it can process data or manage tasks.

The following standards are applied in order to evaluate their performance:

1. The amount of information which can be stored in memory.

2. The computer's internal operations are at a fast pace

3. The quantity and variety of peripheral devices.

4. The computer has various software alternatives from which to pick

In the past, a computer's capacity was mostly determined by its physical size: the larger the machine, the higher the volume. Dimensions, pace of operation, and ratio in computer language are now proportionate. Smaller machines are now produced thanks to recent technological advancements, enabling packaging of comparable speed and versatility in a smaller footprint.

- **Micro Computers:** A revolutionary age in technology began in 1971 with the introduction of mass-produced silicon chips, which made it possible to incorporate computational capabilities into a wide range of equipment. Large-scale integration of silicon chip-powered

microcomputers transformed their capabilities. These chips remarkably reduced the amount of processing power available to tiny sizes; a microprocessor small enough to fit through the eye of a needle serves as evidence of this progress. The creation of semiconductor-based silicon chips was essential to the advancement of microcomputer memories. These microcomputers coordinated stored program control in digital computer systems using a combination of microprocessors, programmable ROM, and RAM. These microcomputers, sometimes referred to as personal computers or PCs, are now widely available and provide compact, affordable solutions for both personal and business use in homes and businesses.

- **Mini Computers:** Thanks to advancements in technology throughout the 1960s, producers were able to meet the growing need for independent devices such as minicomputers, which filled the gap left by larger computers being unfeasible to complete.

Often referred to as mini mainframe computers, these systems offered faster operating speeds and larger storage capacities than their microcomputer equivalents.

Minicomputers combined many desktop drives and were capable of supporting a large number of high-speed input/output devices, which allowed for the direct processing of large data files.

Operating systems designed specifically for minicomputers supported virtual storage and multiprogramming, allowing several applications to run simultaneously. These systems were able to adjust and meet a variety of user needs

because of their inherent flexibility. Although they couldn't match the raw power of larger or medium-sized computers, minicomputers were nonetheless useful because they struck a good balance between size and capabilities, making them a flexible option.

- **Medium-sized Computers:** Compared to smaller computer systems, medium-sized computers provide faster operating speeds and larger storage capacities. Medium-sized computer systems outperform their smaller counterparts in terms of storage capacity and operating performance. The expansion of a computer's data processing capacity by adding extra components, such as memory and peripherals, is what defines its expandability.

- **Large Computers:** These machines represent the pinnacle of speed and adaptability, frequently with minimal user intervention required for control systems. Large computer systems come in a wide range of configurations, from lone processing units to massive national computer networks that integrate massive devices. Large computers' internal operating speeds are expressed in nanoseconds, which highlights their rapidity, while the speeds of smaller computers are expressed in microseconds, which shows a relative difference in processing velocity.

- **Mainframe Computers:** Computers known as mainframes are enormous, multi-user computers designed to process millions of instructions per second and have the capacity to access enormous amounts of data. Because of their skill at handling huge data volumes, they are preferred by big

businesses, airline reservation systems, and hospitals. A mainframe allows users to centrally store vast volumes of data, facilitating processing and access from several computers spread across various locations.

But many find it financially impracticable and prohibitively expensive to purchase a mainframe for personal usage. These systems are usually too expensive and large for individual purchasers to afford. Mainframes are the second largest computers in terms of size and capability among all computer families.

- **Supercomputers:** Supercomputers are the modern equivalent of the ultimate computer power, needed to process massive amounts of data and decipher intricate patterns across many scientific fields. These devices are essential to vital applications like the creation of nuclear weapons and accurate weather forecasting. Their strength is in handling enormous volumes of scientific data, which makes it possible to perform complex physical simulations, quantum physics, weather forecasting, molecular modeling, and climate research.

Supercomputers, which can process hundreds of millions to trillions of instructions per second, are greatly sought after, especially by governments due to their extensive computational capabilities across various domains. They are essential resources for many businesses, helping with everything from product design to animation.

One of the most prominent instances is the PARAM supercomputer series, which was developed by India's

Center for Development of Advanced Computing (CDAC) and boasts astounding processing rates of up to 1 trillion instructions per second. These supercomputers represent the pinnacle of computing technology, facilitating breakthroughs in a variety of fields and advancing scientific and industrial innovation as well as computational intensity.

### **1.2.1 Computer Applications**

#### **Scientific Research**

Computers play a crucial role in scientific research by providing the computational power needed for complex simulations, data analysis, and modeling.

- **Simulations and Modeling:** Used in fields like physics, chemistry, and biology to simulate real-world phenomena, such as climate models, molecular modeling, and astrophysical simulations.

- **Data Analysis:** Processing large datasets from experiments and observations, such as genomic data in bioinformatics or particle collision data in physics.

- **Artificial Intelligence (AI) and Machine Learning (ML):** Applied to identify patterns and make predictions in various scientific disciplines.

#### **Business Applications**

Computers enhance business operations by improving efficiency, accuracy, and decision-making.

- **Office Productivity:** Applications like word processors, spreadsheets, and presentation software help with day-to-day tasks.

- **Enterprise Resource Planning (ERP):** Integrates various business processes like accounting, HR, and supply chain management.

- **Customer Relationship Management (CRM):** Manages interactions with customers, improves customer service, and drives sales growth.

- **Data Analysis and Business Intelligence:** Analyzes business data to support strategic decision-making and identify market trends.

## Education

Computers revolutionize education by providing new learning methods, resources, and tools.

- **E-Learning Platforms:** Online courses, virtual classrooms, and educational software enable remote learning and self-paced education.

- **Multimedia Resources:** Interactive videos, animations, and simulations enhance understanding of complex subjects.

- **Research and Collaboration:** Access to online journals, libraries, and collaborative tools facilitate research and group projects.

- **Administrative Systems:** Manage student information, scheduling, and communication within educational institutions.

## Entertainment

Computers offer a wide range of entertainment options, transforming how people consume media and engage in leisure activities.

- **Gaming:** High-performance computers and gaming consoles support advanced video games with realistic graphics and complex gameplay.

- **Streaming Services:** Platforms like Netflix, YouTube, and Spotify provide on-demand access to movies, TV shows, and music.

- **Social Media:** Websites and applications like Facebook, Instagram, and Twitter connect people and allow for content sharing and communication.

- **Virtual Reality (VR) and Augmented Reality (AR):** Offer immersive experiences in gaming, education, and virtual tours.

## Healthcare

Computers improve patient care, streamline operations, and advance medical research.

- **Electronic Health Records (EHR):** Digitally store patient information, making it easily accessible to healthcare providers.

- **Medical Imaging:** Advanced imaging techniques like MRI, CT scans, and ultrasound rely on computer processing for accurate results.

- **Telemedicine:** Enables remote consultations and monitoring, expanding access to healthcare services.

- **Medical Research:** Analyzes clinical data, supports drug discovery, and helps in understanding diseases through computational biology and bioinformatics.

---

## 1.3 COMPUTER GENERATIONS

---

The development of computers, which started in the sixteenth century, led to the creation of modern technology. The computer that we use now has likewise changed rapidly throughout time.

Computers underwent five major stages known as "Generations of Computers" throughout this time. A new generation of computers has different designs and sizes from their predecessors, but they also have better processing and capabilities. Phase differentiation is determined by the application of switching circuits. These generations include:

- The first generation of computers, which ran from 1940 to 1956.

- The Second Computer Generation ran from 1956 to 1963.

- The Third Generation of Computers, produced between 1964 and 1971.

- Systems that have been around since 1971.

- Computers from the fifth generation forward and beyond.

### First Generation (1940s-1956s)

Vacuum tubes are a defining characteristic of early computers. Filaments were used as an electronic source in the delicate glass apparatus known as a vacuum tube. It is possible through the

manipulation and amplification of electronic impulses. These vacuum tubes were used for control, storage, and calculation. J. created the Electronic Numerical Integrator and Computer (ENIAC), the first electronic computer with a general-purpose programming. John V. Mauchly attends the University of Pennsylvania, as does Presper Eckert. The ENIAC was a 30-foot-long, 30-ton device that required 150,000 watts of electricity to operate. It also had 10,000 capacitors, 70,000 registers, and 18,000 vacuum tubes. Air conditioning was necessary for first-generation computers to function properly since they were too big and unwieldy to install, requiring a huge room. They also used to release a lot of heat. Programs produced in high-level programming languages must be translated into assembly or machine language by a compiler. A program that translates assembly language programs into machine language is called an assembler, also referred to as an assembly language compiler.

Before the ENIAC was finished, Von Neumann created the Electronic Discrete Variable Automatic Computer (EDVAC), which had the ability to store data and programs. The computer operated significantly more swiftly as a result of its immediate access to both data and commands. Another benefit of instruction storage was that it made it possible for computers to reason internally. The 1952 Universal Automatic Computer (UNIVAC), created by Eckert and Mauchly, was thought to be the world's first extremely lucrative computer.

### **Example: UNIVAC-1, EDVAC, and ENIAC**

## **Second Generation (1956s-1963s)**

The underlying technology of the second generation of computers was magnetic core memory combined with solid-state components (transistors and diodes). The transistor may open or close an integrated circuit and magnify signals. It is made of materials known as semiconductors. Transistors are a product of Bell Labs and are utilized in all digital circuits, particularly those in computers. In the initial generation of computers, transistors replaced the heavy electric tubes. Vacuum tubes and transistors are similar in that both use solid materials to transfer electrons instead of a vacuum. Semiconducting material transistors controlled the flow of electricity via the circuit. Simultaneously, they might make computers faster, more powerful, and smaller. They use less electricity, generate less heat, and are less expensive than vacuum tubes. Minimal production costs were also maintained.

The second generation of computers saw the development of the central processor unit (CPU), memory, programming grammar, and input and output devices. Developers were able to define commands in words by switching from the mysterious binary machine syntax to figurative, or assembly, languages in gadgets of the second generation. These were the first systems to use magnetic core architecture instead of magnetic drum technology, and they were also the first to store programs in memory. High-level programming languages like FORTRAN (1956), ALGOL (1958), and COBOL (1959) were created during the second generation.

PDP-8, IBM 1400 series, IBM 1620, IBM 7090, and CDC 3600 are a few examples.

### **Third Generation (1964s-1971s)**

Third-generation computers were first released in 1964. The efficiency and productivity of computers were significantly increased by the placement and shrinking of transistors on silicon chips, commonly known as semiconductors. Integrated Circuits were used by them (ICs).

A turning point in the development of computers and technology was the discovery of integrated circuits. Chips is the term used to describe these integrated circuits.

Due to its atomic structure, silicon is a great semiconductor element that is utilized as a building block for the production of semiconductors, computer chips, silicon diodes, and other electrical circuits and switching devices. It is possible to introduce or mix silicon with other elements—like phosphorous, arsenic, or boron—to alter its conductive properties. A typical chip, which is smaller than 14 square inches, can have millions of transistors and other electrical components on it. Printed circuit boards, which are electronic panels, are used in computers to hold a large number of chips. There are numerous varieties of chips. Microprocessors, or CPU chips, are capable of processing an entire system, whereas memory chips are limited to storing blank memory.

Many transistors, records, and resistors assembled on a single thin silicon sheet make form an integrated circuit (IC). Two methods for creating integrated circuits are medium-scale insertion (MSI) and small-scale inclusion (SSI). The advent of multilayer printed circuitry and the replacement of slower core memory with faster solid-state memories superseded core memory. Because it can

integrate multiple circuits into a single chip, IC technology was also known as microelectronics technology.

This generation of machines has very fast processing speeds, a big amount of memory, low cost, and small size. During this time, more sophisticated languages were developed, such as Basic (Beginners All-purpose Symbolic Instruction Code).

This generation's main advantages included new input/output devices, improved secondary storage devices, and solid-state circuitry. The speed of the computer increased with the extra circuitry. During this era, minicomputers were also developed.

A few examples are IBM 360,370, B6500, and NCR 395. These days, arithmetic and logical operations could be finished in nanoseconds or microseconds.

#### **Fourth Generation (1970s-Present)**

In 1971, fourth-generation computers were introduced as a result of the creation of computing components using large scale integration (LSI). Microprocessors are silicon devices used to generate LSI circuits. The circuitry needed to carry out arithmetic, logic, and control functions on a single chip is found in a microprocessor. The fourth generation of computers can calculate more than equivalent-sized third-generation computers because of microprocessors. The ability to fit a computer's central processing unit (CPU) on a single semiconductor is made possible by advancements in microprocessor technology. We refer to these devices as microcomputers. In the past, VLSI circuits mostly replaced LSI circuits.

In the first generation, something might have required a full room, but it might now fit in your palm. When the Intel 4004 microprocessor was created in 1971, it included every component of a computer, including the input/output controllers, storage, and main processing unit.

Microelectronics and other computer technologies, such as multiprocessing, multiprogramming, time-sharing, quick operation, and cloud storage, were the main innovations of this generation. High-speed vector processors at this period changed the paradigm for high-performance computing. Most time-shared mainframe systems were equipped with workstations and microcomputers. Consequently, the computer that was once somewhat large may now be set up on a table. It is a fourth-generation computer, the personal computer.

Throughout this time, computer networks developed.

**Examples are Alter 8800 and Apple II.**

### **Fifth Generation (Present and Beyond)**

Artificial intelligence-powered fifth-generation computers are still in the development stages, although they have already been used for various tasks, like speech recognition. Artificial Intelligence (AI) is a subfield of computer science that focuses on teaching machines to think and behave like people. Computers are now unable to fully exhibit artificial intelligence, or to mimic human behavior. The most advancements have been made in the gaming sector. Right now, the best computer chess programs are able to defeat human players. The fastest-growing area of computational intelligence is artificial neural networks, which have shown

promise in a number of applications including speech recognition and natural language processing.

AI languages are frequently referred to as programming languages because they are typically utilized for AI applications. The two most popular ones are LISP and Prolog. The fifth generation of computers is incredibly fast. Developers turned their primary attention to parallel processing in their research and development of fifth-generation computers. Up until recently, vector computations and pipeline construction were the only tasks that could be done in parallel. Machines with hundreds of processors were introduced in this age, enabling them to work on different portions of a same program. The development of ever-more-powerful computing devices is still ongoing. This kind of computer is expected to be able to converse with its user in plain language, retain enormous knowledge bases, search through them rapidly, make deft decisions, and come to logical conclusions.

---

## **1.4 NUMBER SYSTEM**

---

Words and characters make up the language that we speak to one another. Words, letters, and numbers make sense to us. Computers are not meant to handle this kind of data, though. Only numbers are understood by computers.

Thus, data is turned into electronic pulses when entered. Every pulse is recognized as a code, which ASCII then converts into a numeric format. It assigns a numerical value (number) that a computer can comprehend to each number, character, and symbol.

Therefore, one needs to be knowledgeable with number systems in order to grasp the language of computers.

Computers employ one of the following number systems:

- Binary number system

- Octal number system

- Decimal number system

- Hexadecimal number system

## 1. Binary System (Base 2)

The binary system uses only two digits, 0 and 1, to represent numbers. It is the foundation of all modern computing systems because computers operate using binary logic.

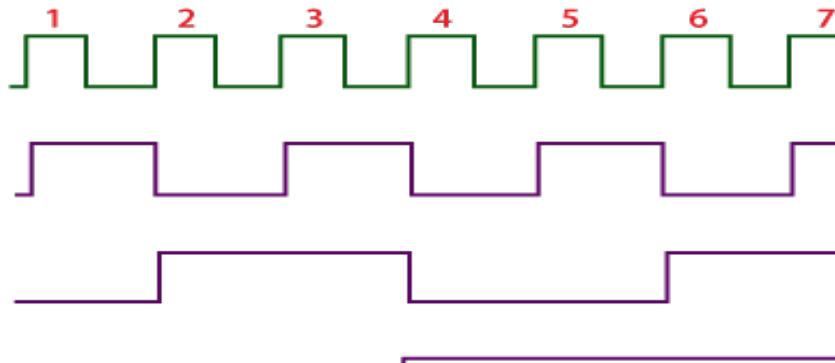

Its base is two because it only has the numbers "0" and "1." As a result, there are only two kinds of electronic pulses in this number system: those that indicate "0" and "1," respectively, and those that do not. A bit is a single digit. A byte (11001010) is a group of eight bits, whereas a nibble is a group of four bits (1101). Each binary number's place corresponds to a certain power of the number system's base (2).

- **Advantages:** Direct correspondence with digital logic and electronic devices.

- **Disadvantages:** Lengthy illustration for massive numbers, limited expressiveness for decimal fractions.

## 2. Octal System (Base 8)

The octal system uses eight digits, from 0 to 7, to represent numbers. It is often used as a shorthand representation of binary numbers since 8 is a power of 2.

Its base is eight since it consists of eight digits (0, 1, 2, 3, 4, 5, 6, 7). An octal number's digits each correspond to a certain power of its base (8). Any octal number may be converted into a binary number using the three bits ( $2^3 = 8$ ) of the binary number system, since there are only eight digits. Long binary numbers can also be shortened using this number method. A single octal digit can represent all three binary digits.

- **Advantages:** Consolidated example of binary values, readability, especially contexts.

- **Disadvantages:** Less usually used, more intuitive than hexadecimal.

## 3. Decimal System (Base 10)

This number system's base is ten since it has ten digits: 0, 1, 2, 3, 4, 5, 6, 7, 8, 9. The highest value of a digit in this number system is nine, while the lowest value is zero. Each digit in a decimal number indicates a certain power of the number system's base (10) at that point. We frequently utilize this number system in our daily lives. It can be used to represent any number.

- **Advantages:** Easily understandable, modern for vast arithmetic.

- **Disadvantages:** Inadequate for binary data, constrained expressiveness for non-decimal fractions.

## 4. Hexadecimal System (Base 16)

The hexadecimal system uses sixteen digits, from 0 to 9 and A to F (where A=10, B=11, F=15), to represent numbers. It is commonly used in computing as a more human-friendly representation of binary-coded values.

There are 16 digits in this numeral system, ranging from 0 to 9 and A to F. Thus, sixteen is its basis. 10 to 15 decimal places are represented by the alphabets A through F. A hexadecimal integer's location corresponds to a certain power of base (16) in the number system. Any hexadecimal number may be converted into a binary number using the four bits (2<sup>4</sup>=16) of the binary number system, since there are only sixteen digits. Because it employs both alphabets and numeric digits, it is often referred to as the alphanumeric number system.

- **Advantages:** Compact representation of binary, widely utilized in programming.

- **Disadvantages:** Intimidating for beginners, decimal is more user-friendly than hexadecimal.

### Importance of Number Systems in Computer Science

In computer technology, it is crucial to comprehend specific range structures for a number of reasons.

- **Memory Management:** Binary systems are used by computers to manage their memory. Being able to convert between binary, octal, decimal, and hexadecimal allows one to work with memory and storage in an efficient manner.

- **Programming:** Hexadecimal is frequently used in programming to represent binary-coded numbers and memory addresses. For bitwise operations, octal and binary representations are essential.

- **Data Transmission:** In computer architecture, binary is crucial for record transmission. Miles are often converted to binary for processing efficiency when records are saved or sent.

- **Debugging:** Hexadecimal is a low-level programming language that is typically used in debugging. Hexadecimal format is often used for memory dumps and machine code.

- **Digital electronics:** Since circuits in this field are mostly based on binary signals, it is necessary to understand binary.

- **Representation of Colors:** Hexadecimal is widely used in graphics and web development to represent colorations. A set of hexadecimal digits is used to represent each RGB coloration element.

- **Hashing and Encryption:** Binary models are necessary in cybersecurity since many hash tables and encryption methods process binary data.

---

## 1.5 CONVERSION TECHNIQUES

---

- **Binary to Octal:** Group binary digits in sets of three, starting from the right.

Example: Convert binary 1011 to decimal.

Solution:

$$\begin{aligned}1011_2 &= 1 \times 2^3 + 0 \times 2^2 + 1 \times 2^1 + 1 \times 2^0 \\&= 1 \times 8 + 0 \times 4 + 1 \times 2 + 1 \times 1 \\&= 8 + 0 + 2 + 1 \\&= 11_{10}\end{aligned}$$

- **Decimal to Binary**

Example: Convert decimal 13 to binary.

Solution:

- Divide 13 by 2: quotient = 6, remainder = 1

- Divide 6 by 2: quotient = 3, remainder = 0

- Divide 3 by 2: quotient = 1, remainder = 1

- Divide 1 by 2: quotient = 0, remainder = 1

Read remainders in reverse order: 1101

So,  $13_{10} = (1101)_2$

- **Octal to Decimal**

Example: Convert octal 21 to decimal.

Solution:

$$\begin{aligned}21_8 &= 2 \times 8^1 + 1 \times 8^0 \\&= 2 \times 8 + 1 \times 1 \\&= 16 + 1 \\&= 17_{10}\end{aligned}$$

- **Decimal to Octal**

Example: Convert decimal 29 to octal.

Solution:

- Divide 29 by 8: quotient = 3, remainder = 5

- Divide 3 by 8: quotient = 0, remainder = 3

Read remainders in reverse order: 35

So,  $29_{10} = 35_8$

- **Hexadecimal to Decimal**

Example: Convert hexadecimal 1F to decimal.

Solution:

$$1F_{16} = 1 \times 16^1 + F \times 16^0$$

(Note:  $F = 15$ )

$$= 1 \times 16 + 15 \times 1$$

$$= 16 + 15$$

$$= 31_{10}$$

- **Decimal to Hexadecimal**

Example: Convert decimal 47 to hexadecimal.

Solution:

- Divide 47 by 16: quotient = 2, remainder = 15 (F in hexadecimal)

- Divide 2 by 16: quotient = 0, remainder = 2

Read remainders in reverse order: 2F

So,  $47_{10} = 2F_{16}$

- **Binary to Octal**

Example: Convert binary 110110 to octal.

Solution:

- Group binary digits in sets of three, starting from the right: 110 110

- Convert each group to its octal equivalent:

- $110_2 = 6_8$

- $110_2 = 6_8$

So,  $110110_2 = 66_8$

- **Octal to Binary**

Example: Convert octal 73 to binary.

Solution:

- Convert each octal digit to its three-digit binary equivalent:

- $7_8 = 111_2$

- $3_8 = 011_2$

Combine the binary groups: 111011

So,  $73_8 = 111011_2$

- **Binary to Hexadecimal**

Example: Convert binary 101101 to hexadecimal.

Solution:

- Group binary digits in sets of four, starting from the right: 0010 1101

- Convert each group to its hexadecimal equivalent:

- $0010_2 = 2_{16}$

- $1101_2 = D_{16}$

So,  $101101_2 = 2D_{16}$

- **Hexadecimal to Binary**

Example: Convert hexadecimal 3A to binary.

Solution:

1. Convert each hexadecimal digit to its four-digit binary equivalent:

- $3_{16} = 0011_2$

- $A_{16} = 1010_2$

Combine the binary groups: 00111010

So,  $3A_{16} = 00111010_2$

Number System Relationship

The following table depicts the relationship between decimal, binary, octal and hexadecimal number systems.

| HEXADECIMAL | DECIMAL | OCTAL | BINARY |

|-------------|---------|-------|--------|

| 0           | 0       | 0     | 0000   |

| 1           | 1       | 1     | 0001   |

| 2           | 2       | 2     | 0010   |

| 3           | 3       | 3     | 0011   |

| 4           | 4       | 4     | 0100   |

| 5           | 5       | 5     | 0101   |

| 6           | 6       | 6     | 0110   |

| 7           | 7       | 7     | 0111   |

| 8           | 8       | 10    | 1000   |

| 9           | 9       | 11    | 1001   |

| A           | 10      | 12    | 1010   |

| B           | 11      | 13    | 1011   |

| C           | 12      | 14    | 1100   |

| D           | 13      | 15    | 1101   |

| E           | 14      | 16    | 1110   |

| F           | 15      | 17    | 1111   |

---

## 1.6 CHARACTER CODES

---

Character codes are a way to represent characters, such as letters, digits, and symbols, using numerical codes. These codes are used by computers to store, process, and communicate text data. Each character is assigned a unique numerical value, known as a code

point, which is used to represent that character in computer systems.

### **Why are Character Codes used?**

Character codes are essential in computing because they enable:

1. **Text Storage:** Computers can store text data efficiently using numerical codes, which take up less space than the actual characters.

2. **Text Processing:** Character codes allow computers to perform operations on text data, such as sorting, searching, and manipulating text.

3. **Communication:** Character codes enable different computer systems to communicate with each other, by providing a standard way to represent text data.

4. **Encoding:** Character codes are used to encode text data into a format that can be transmitted over networks, stored on devices, and displayed on screens.

5. **Decoding:** Character codes are used to decode encoded text data back into its original form, allowing computers to interpret and display text correctly.

**There are some character code given below:**

#### **BCD (Binary-Coded Decimal)**

BCD is a way to represent decimal numbers using binary code. It uses 4 bits to represent each decimal digit, with each bit corresponding to a decimal value.

Representation:

| Decimal Digit | BCD Representation |

|---------------|--------------------|

| 0             | 0000               |

| 1             | 0001               |

| 2             | 0010               |

| 3             | 0011               |

| 4             | 0100               |

| 5             | 0101               |

| 6             | 0110               |

| 7             | 0111               |

| 8             | 1000               |

| 9             | 1001               |

**Example:** The decimal number 123 would be represented in BCD as:

0001 0010 0011

**Usage:** BCD is commonly used in financial and commercial applications, such as accounting and inventory management.

**Limitations:** BCD is less efficient than binary representation, as it requires more bits to represent the same number.

### ASCII (American Standard Code for Information Interchange)

ASCII is a character encoding standard that represents text data using binary code. It assigns a unique binary code to each character, including letters, digits, and special characters.

**ASCII Table:**

| Character | ASCII Code |

|-----------|------------|

| A         | 65         |

| B         | 66         |

| C         | 67         |

| ...       | ...        |

| a         | 97         |

| b         | 98         |

| c         | 99         |

| ...       | ...        |

| 0         | 48         |

| 1         | 49         |

| 2         | 50         |

| ...       | ...        |

| !         | 33         |

| @         | 64         |

| #         | 35         |

**Significance:** ASCII is widely used in computers and devices to represent text data. It is the basis for many other character encoding standards.

**Example:** The string "Hello" would be represented in ASCII as:

H - 72

e - 101

l - 108

l - 108

o - 111

**EBCDIC (Extended Binary Coded Decimal Interchange Code)**

EBCDIC is a character encoding standard developed by IBM for their mainframe computers. It is an extension of the BCD code, with additional characters and symbols.

**Representation:** EBCDIC uses 8 bits to represent each character, with the first 4 bits representing the zone (category) and the last 4 bits representing the digit or character.

**Comparison with ASCII:**

- EBCDIC is specific to IBM mainframes, while ASCII is widely used across different platforms.

- EBCDIC has a larger character set than ASCII, including additional symbols and graphics.

- EBCDIC is less efficient than ASCII, requiring more bits to represent the same character.

**Example:** The string "Hello" would be represented in EBCDIC as:

H - 200

e - 109

l - 121

l - 121

o - 147

---

## 1.7 CONCLUSION

---

As we conclude this unit, we reflect on the significant journey we've undertaken to explore the fundamental concepts of computers. From the basic components that make up a computer system to the various applications that have transformed the way

we live, work, and communicate, we've gained a deeper understanding of the technology that drives our modern world.

We've traced the evolution of computers through the generations, from the early mainframes to the sleek, portable devices of today, and examined the number systems and character codes that enable computers to process and store information. We've seen how computers have revolutionized industries, transformed businesses, and connected people across the globe.

Through this unit, we've developed a solid foundation in computer fundamentals, which will serve as a springboard for further learning and exploration in the field of computer science. We've acquired a vocabulary of key terms and concepts, a understanding of the underlying principles, and a appreciation for the impact of computers on our daily lives.

As we move forward in this rapidly changing digital landscape, we're equipped with the knowledge and skills to navigate the exciting world of computers and technology. We're prepared to embrace new technologies, to innovate, and to shape the future of computing. The journey ahead promises to be thrilling, and we're ready to take on the challenges and opportunities that come our way.

---

## **1.8 UNIT BASED QUESTIONS & ANSWERS**

---

1. What is the basic component of a computer system that performs calculations and executes instructions?

Answer: The Central Processing Unit (CPU) is the brain of the computer and performs calculations, executes instructions, and controls the other components. It takes in instructions, decodes them, and carries out the necessary actions.

2. Which generation of computers introduced the use of transistors?

Answer: The second generation of computers (1956-1963) introduced the use of transistors, which replaced vacuum tubes. Transistors were smaller, faster, and more reliable, leading to significant improvements in computer performance.

3. What is the binary number system based on?

Answer: The binary number system is based on two digits: 0 and 1. This system uses bits (binary digits) to represent information, with each bit having a value of either 0 or 1. Binary is the fundamental language of computers.

4. What is the purpose of character codes in computing?

Answer: Character codes are used to represent characters, such as letters, symbols, and digits, using numerical codes. This allows computers to store, process, and communicate text data efficiently.

5. What is the most common character code used in computing?

Answer: ASCII (American Standard Code for Information Interchange) is the most widely used character code in computing. It assigns a unique numerical value to each character, making it possible for computers to understand and exchange text data.

6. What is the process of converting data from one number system to another called?

Answer: The process of converting data from one number system to another is called data conversion or numerical conversion. This is necessary when working with different computer systems or programming languages that use different number systems.

---

## 1.9 REFERENCES

---

- "Advanced Computer Architecture: Parallelism, Scalability, Programmability" by Hwang, Kai

- "Computer Applications In Management" Dahiya, U/ Nagpal, S.

- "Computer Applications With C & C++: With Programs & Numerical Problems" Abhyankar, A. K.

- "Computer Architecture & Organization" Hayes, J. P.

- "Computer Data-base Organization" Martin, James

- "Computer Graphics" Hearn, D/ Baker, M.

---

## **UNIT – 2: BASICS OF CIRCUITS**

---

### **Structure**

- 2.0 Introduction

- 2.1 Objectives

- 2.2 Logic Gates

- 2.3 Boolean Algebra

- 2.4 K-map Simplification

- 2.4.1 2-Variable K-map

- 2.4.2 3-variable K-map

- 2.4.3 The 4-Variable Karnaugh Map

- 2.4.4 Don't Care Conditions

- 2.5 Half Adder

- 2.6 Full Adder

- 2.7 Multiplexer

- 2.8 Demultiplexer

- 2.9 Decoder

- 2.10 Encoders

- 2.11 Conclusion

- 2.12 Unit Based Questions & Answers

- 2.13 References

---

## **2.0 INTRODUCTION**

---

In digital electronics and computer engineering, understanding fundamental concepts such as logic gates, Boolean algebra, and combinational circuits is essential. These concepts form the backbone of modern computing systems, enabling the design and implementation of complex circuits that perform various tasks efficiently and reliably.

This unit delves into several key components and techniques within digital electronics. Starting with an exploration of logic gates, which are the basic building blocks of digital circuits, we move on to Boolean algebra—a mathematical framework used to analyze and design these circuits. The unit further covers Karnaugh map (K-map) simplification techniques, which offer systematic methods for minimizing Boolean expressions.

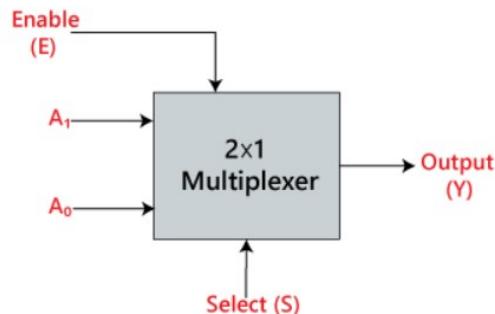

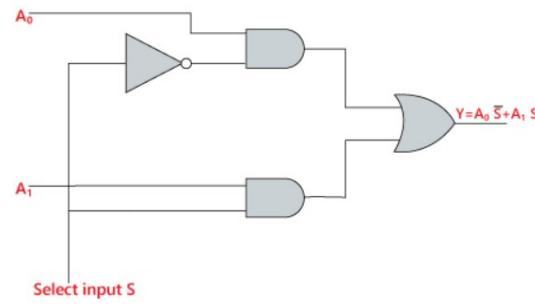

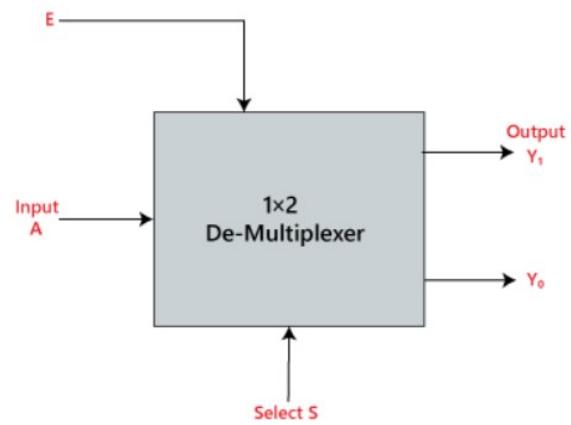

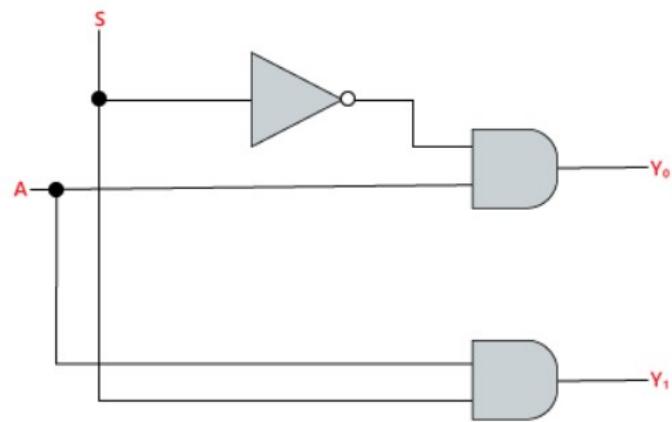

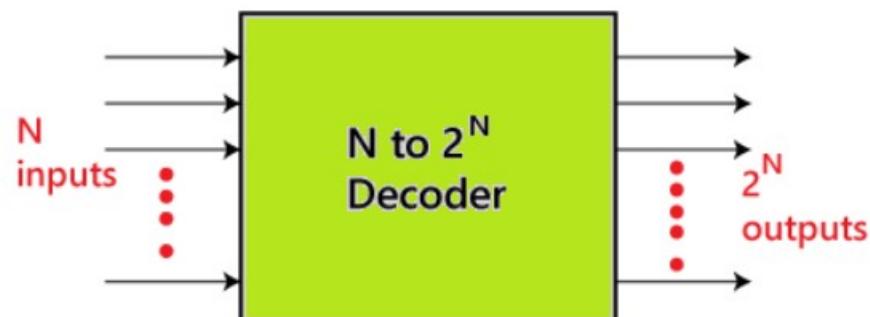

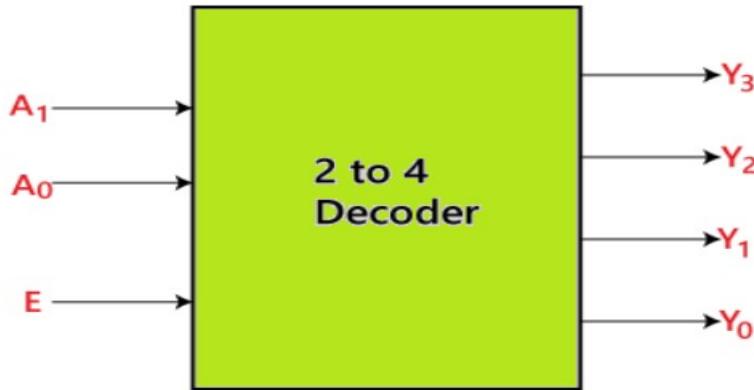

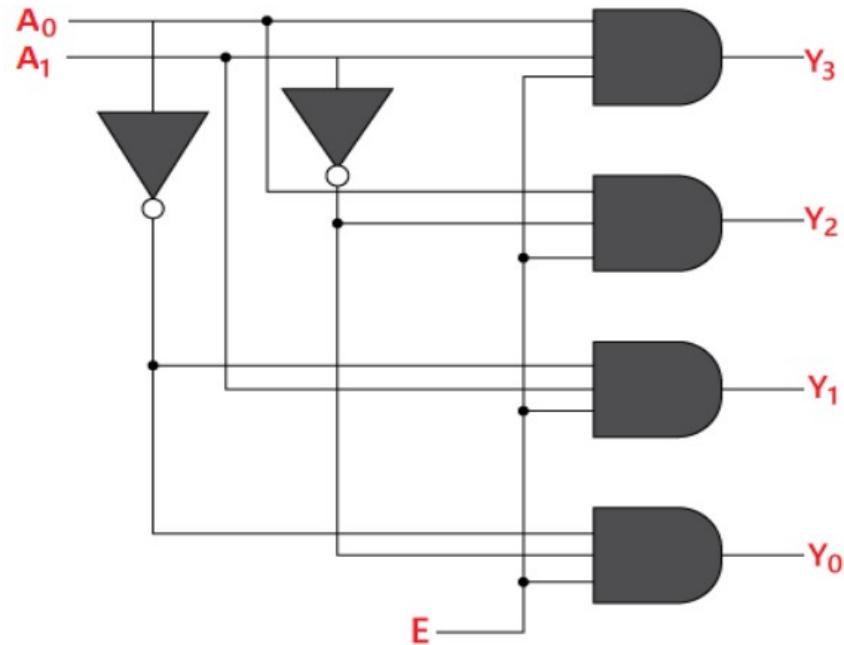

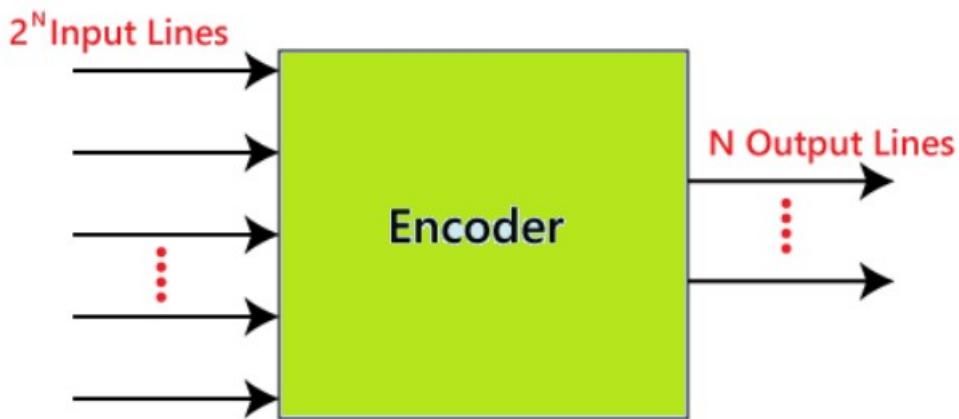

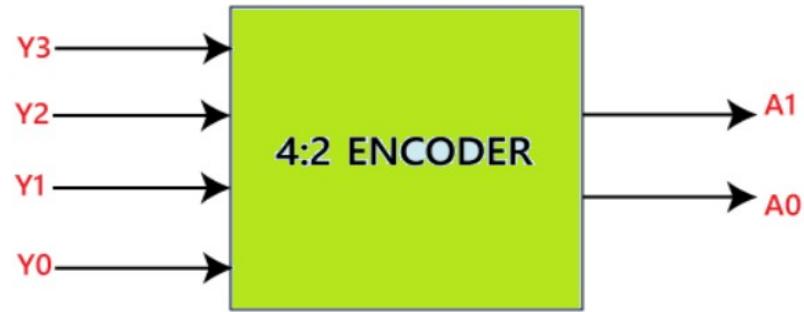

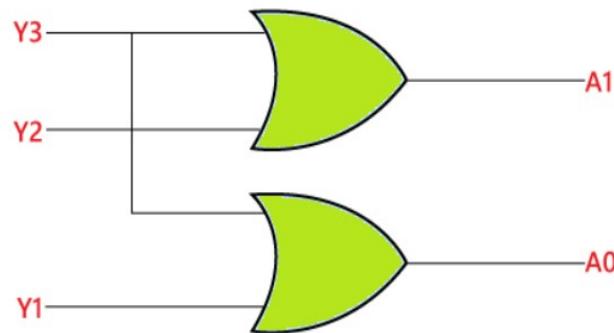

Combinational circuits like half adders and full adders are introduced, illustrating how simple logic elements can perform arithmetic operations crucial for computing. Multiplexers and demultiplexers are then explored, demonstrating their roles in data selection and distribution within digital systems. Decoders and encoders are discussed next, highlighting their applications in tasks such as memory addressing and data conversion.

Through a structured approach, this unit aims to provide a comprehensive understanding of these foundational concepts and their practical applications in digital electronics. Unit-based questions and answers are included to reinforce learning and assessment, ensuring a thorough grasp of the material covered.

---

## 2.1 OBJECTIVES

---

After completing this unit, students will be able to understand,

- **Understand Logic Gates:** Explore the fundamental types of logic gates (AND, OR, NOT, NAND, NOR, XOR, XNOR) and their truth tables.

- **Apply Boolean Algebra:** Apply Boolean laws and theorems (commutative, associative, distributive, De Morgan's) to simplify Boolean expressions.

- **Master K-map Simplification:** Learn the concept of Karnaugh maps (K-maps) and their importance in simplifying Boolean expressions.

- **Study Half Adder and Full Adder:** Understand the structure and operation of half adders and full adders.

- **Explore Multiplexers (MUX) and Demultiplexers (DEMUX):** Define the function and operation of multiplexers in selecting one of several input signals based on a control signal.

---

## 2.2 LOGIC GATES

---

Logic gates are the building blocks of digital electronics and computer systems. They are electronic circuits that perform logical operations on one or more input signals to produce an output signal. There are seven basic types of logic gates: AND, OR, NOT, NAND, NOR, XOR, and XNOR.

### 1. AND Gate

The AND gate produces an output of 1 only if all the input signals are 1.

#### Truth Table:

| <b>A</b> | <b>B</b> | <b>Output</b> |

|----------|----------|---------------|

| 0        | 0        | 0             |

| 0        | 1        | 0             |

| 1        | 0        | 0             |

| 1        | 1        | 1             |

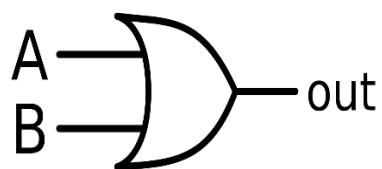

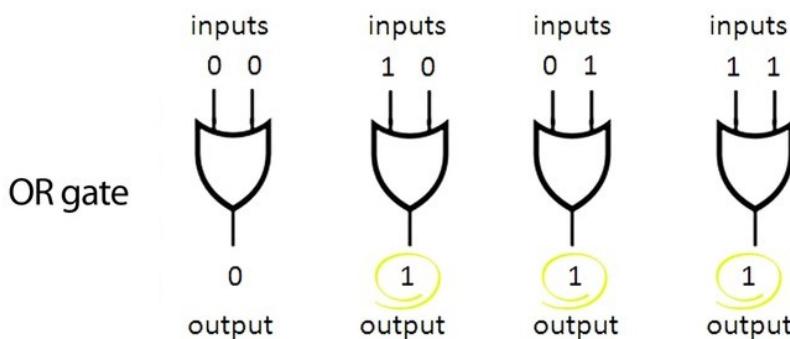

## 2. OR Gate

The OR gate produces an output of 1 if any of the input signals are

1.

### Truth Table:

| <b>A</b> | <b>B</b> | <b>Output</b> |

|----------|----------|---------------|

| 0        | 0        | 0             |

| 0        | 1        | 1             |

| 1        | 0        | 1             |

| A | B | Output |

|---|---|--------|

| 1 | 1 | 1      |

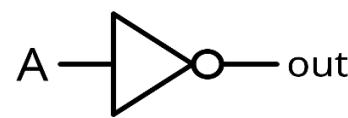

### 3. NOT Gate (Inverter)

The NOT gate produces an output that is the opposite of the input signal.

Truth Table:

| A | Output |

|---|--------|

| 0 | 1      |

| 1 | 0      |

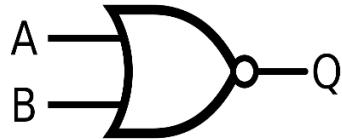

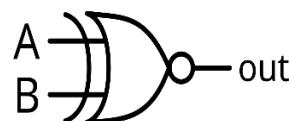

### 4. NAND Gate

The NAND gate produces an output of 1 only if none of the input signals are 1.

Truth Table:

| A | B | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

## 5. NOR Gate

The NOR gate produces an output of 1 if all the input signals are 0.

Truth Table:

| A | B | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| 1 | 0 | 0      |

| 1 | 1 | 0      |

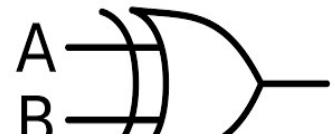

## 6. XOR Gate

The XOR gate produces an output of 1 if the input signals are different.

Truth Table:

| A | B | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

## 7. XNOR Gate

The XNOR gate produces an output of 1 if the input signals are the same.

Truth Table:

| A | B | Output |

|---|---|--------|

| 0 | 0 | 1      |

| 0 | 1 | 0      |

| A | B | Output |

|---|---|--------|

| 1 | 0 | 0      |

| 1 | 1 | 1      |

## Gate-Level Minimization

Gate-Level Minimization (GLM) is a technique used to simplify digital circuits by reducing the number of logic gates required to implement a particular function. The goal is to minimize the complexity of the circuit while maintaining its functionality.

### GLM involves:

1. **Simplifying Boolean expressions:** Using laws and theorems of Boolean algebra to simplify the Boolean expression representing the digital circuit.

2. **Removing redundant gates:** Identifying and removing gates that don't affect the output of the circuit.

3. **Combining gates:** Merging multiple gates into a single gate or a smaller number of gates.

4. **Optimizing gate configuration:** Reconfiguring the gates to reduce the overall number of gates and improve performance.

**Some common techniques used in GLM include:**

1. **Karnaugh Maps (K-maps):** A graphical method for simplifying Boolean expressions and identifying prime implicants.

2. **Quine-McCluskey Algorithm:** A tabular method for minimizing Boolean expressions.

3. **Espresso Algorithm:** A computer-aided design (CAD) tool for minimizing digital circuits.

**GLM is important because it:**

1. **Reduces circuit complexity:** Fewer gates mean less power consumption, reduced area, and increased performance.

2. **Improves reliability:** Less complex circuits are less prone to errors and faults.

3. **Reduces cost:** Fewer gates and reduced complexity lead to lower manufacturing costs.

Gate-level minimization is the process of simplifying a digital circuit to reduce the number of gates and improve performance. This can be done using various techniques such as:

- Karnaugh maps (K-maps)

- Quine-McCluskey algorithm

- Espresso algorithm

These techniques help to minimize the number of gates required to implement a digital circuit, reducing the overall cost and improving performance.

---

## 2.3 BOOLEAN ALGEBRA

---

Boolean algebra is a branch of mathematics that deals with logical operations and their representations. It is named after George Boole, who introduced this concept in the mid-19th century. Boolean algebra is used to analyze and simplify digital circuits, computer networks, and logical statements. It consists of logical operators, variables, and constants that follow specific rules and laws.

### Boolean Laws and Theorems

Boolean laws and theorems are fundamental properties that govern Boolean algebra. These laws and theorems help in simplifying and manipulating Boolean expressions. Here are some of the key Boolean laws and theorems:

Here are all the Boolean laws:

#### 1. Commutative Laws

- OR:  $A + B = B + A$

- AND:  $AB = BA$

#### 2. Associative Laws

- OR:  $(A + B) + C = A + (B + C)$

- AND:  $(AB)C = A(BC)$

#### 3. Distributive Laws

- OR:  $A(B + C) = AB + AC$

- AND:  $A + BC = (A + B)(A + C)$

#### 4. Identity Laws

- OR:  $A + 0 = A$

- AND:  $A1 = A$

- OR:  $A + 1 = 1$

- AND:  $A0 = 0$

### 5. Complement Laws

- $!A = A'$

- $!!A = A$

### 6. Involution Law

- $(A')' = A$

### 7. De Morgan's Laws

- $!(A + B) = !A!B$

- $!(AB) = !A + !B$

### 8. Absorption Laws

- $A(A + B) = A$

- $A + AB = A$

### 9. Simplification Laws

- $A + !A = 1$

- $A!A = 0$

### 10. Consensus Laws

- $AB + !AC = AB + C$

- $A + BC = A + !AB + C$

### 11. Boolean Algebra Theorems

- $(A + B)(A' + B') = AA' + BB'$

- $(A + B)(A + B') = A$

### Boolean Expressions and Equation Simplification

Boolean expressions are formed using logical operators, variables, and constants. Simplifying Boolean expressions involves applying Boolean laws and theorems to reduce the complexity of the expression.

- **Simplification:** Simplifying a Boolean expression means reducing it to its simplest form without changing its original meaning.

- **Equation:** A Boolean equation is a statement that two Boolean expressions are equal.

Simplification techniques include:

- Removing redundant parentheses

- Applying De Morgan's theorem

- Using distributive law

- Combining like terms

### **Example for the simplification:**

Simplifying Boolean expressions and equations involves applying Boolean laws and theorems to reduce the complexity of the expression. Here are some examples:

#### Example 1: Simplifying a Boolean Expression

$$\text{Expression: } (A + B)(A + C)$$

Step 1: Apply the distributive law

$$(A + B)(A + C) = A(A + C) + B(A + C)$$

Step 2: Simplify

$$A(A + C) + B(A + C) = A^2 + AC + AB + BC$$

Step 3: Remove redundant terms ( $A^2 = A$ )

$$A^2 + AC + AB + BC = A + AC + AB + BC$$

Simplified Expression:  $A + AC + AB + BC$

#### Example 2: Simplifying a Boolean Equation

$$\text{Equation: } AB + AC = A(B + C)$$

Step 1: Apply the distributive law

$$A(B + C) = AB + AC$$

Step 2: Equate the two expressions

$$AB + AC = AB + AC$$

Simplified Equation: True (the equation is always true)

Example 3: Simplifying a Boolean Expression with De Morgan's Theorem

Expression:  $!(A + B)$

Step 1: Apply De Morgan's theorem

$$!(A + B) = !A!B$$

Simplified Expression:  $!A!B$

Example 4: Simplifying a Boolean Equation with Redundant Parentheses

$$\text{Equation: } (A + B) + C = A + (B + C)$$

Step 1: Remove redundant parentheses

$$(A + B) + C = A + B + C$$

Step 2: Equate the two expressions

$$A + B + C = A + B + C$$

**Simplified Equation: True (the equation is always true)**

These examples demonstrate how to simplify Boolean expressions and equations using Boolean laws and theorems. By applying these techniques, we can reduce the complexity of Boolean expressions and equations, making them easier to analyze and understand.

---

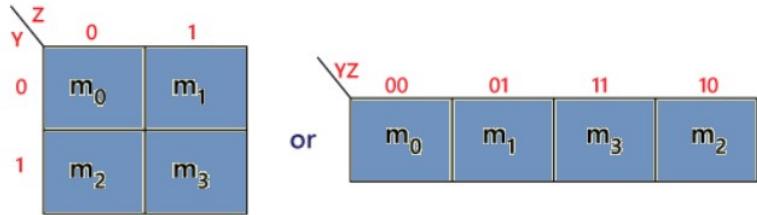

## 2.4 K- MAP SIMPLIFICATION

---

Boolean expressions can be systematically made simpler with the K-map. The minimal expression, which is the simplest POS and SOP expression, can be found with the aid of the K-map approach. A simplified cookbook is offered by the K-map.

A K-map, like a truth table, lists every possible combination of input variable values and matching output values. In K-map, on the other hand, the values are kept in the array's cells. Every input variable has a binary value that is kept in each cell.

When creating expressions with 2, 3, 4, and 5 variables, the K-map approach is employed. The Quine-McClusky approach is another technique for simplification that is utilized for bigger numbers of variables. The total number of variable input combinations is comparable to the number of cells in a K-map. For instance, if there are three variables, there are  $2^3=8$  cells, and if there are four variables, there are 16 cells. K-map accepts both the POS and SOP versions. The 0s and 1s are used to fill the K-map grid. Creating groups is the solution to the K-map.

The expressions are solved using K-map in the following steps:

- Initially, we determine the K-map based on the quantity of variables.

- Determine the expression's maxterm and minterm.

- Put 1 in each of the K-map's SOP cells corresponding to the minterms.

- Put 0 in the block's POS cells corresponding to the maxterm.

- Next, we aim to cover as many elements as we can in a single group by forming rectangular groups with total terms in the power of two, such as 2, 4, 8,...

- We locate the product words and compile them into the SOP form with the aid of these groupings.

### 2.4.1 2-Variable K-map

There is a total of 4 variables in a 2-variable K-map. There are two variables in the 2-variable K-map. The following figure shows the structure of the 2-variable K-map:

- There is only one way to arrange four neighboring minterms in the above image.

- Grouping two adjacent minterms can take the following forms:  $\{(m_0, m_1), (m_2, m_3), (m_0, m_2), \text{ and } (m_1, m_3)\}$ .

### 2.4.2 3-variable K-map

An array with eight cells represents the three-variable K-map. In this instance, the variables were A, B, and C. Any letter can be used to represent a variable in its name. Variables A and B's binary values are on the left, whereas variable C's values are across the top. The binary values of A and B at the left side of the same row paired with the value of C at the top of the same column make up the value of the given cell. For instance, the binary values of the cells in the bottom right corner and upper left corners, respectively, are 101 and 000, respectively.

|    |    | C |   |

|----|----|---|---|

|    |    | 0 | 1 |

| AB | 00 | 0 | 1 |

|    | 01 | 0 | 1 |

| AB | 11 | 0 | 1 |

|    | 10 | 0 | 1 |

|    |    | C                       |                   |

|----|----|-------------------------|-------------------|

|    |    | 0                       | 1                 |

| AB | 00 | $\bar{A}\bar{B}\bar{C}$ | $\bar{A}\bar{B}C$ |

|    | 01 | $\bar{A}B\bar{C}$       | $\bar{A}BC$       |

| AB | 11 | $A\bar{B}\bar{C}$       | $ABC$             |

|    | 10 | $A\bar{B}C$             | $A\bar{B}\bar{C}$ |

### 2.4.3 The 4-Variable Karnaugh Map

An array of 16 cells represents the 4-variable K-map. The binary values of C and D are across the top, and A and B are down the left. The binary values of A and B at the left side of the same row paired with the binary values of C and D at the top of the same column represent the value of the given cell. For instance, the binary values of the cells in the lower right corner (1010) and upper right corner (0010) are respectively.

|    |    | CD |    |    |    |

|----|----|----|----|----|----|

|    |    | 00 | 01 | 11 | 10 |

| AB | 00 | 0  | 1  | 1  | 0  |

|    | 01 | 0  | 0  | 0  | 0  |

| AB | 11 | 0  | 0  | 0  | 0  |

|    | 10 | 0  | 0  | 0  | 0  |

|    |    | CD                             |                          |                    |                    |

|----|----|--------------------------------|--------------------------|--------------------|--------------------|

|    |    | 00                             | 01                       | 11                 | 10                 |

| AB | 00 | $\bar{A}\bar{B}\bar{C}\bar{D}$ | $\bar{A}\bar{B}C\bar{D}$ | $\bar{A}\bar{B}CD$ | $\bar{A}BC\bar{D}$ |

|    | 01 | $\bar{A}B\bar{C}\bar{D}$       | $\bar{A}B\bar{C}D$       | $\bar{A}BCD$       | $\bar{A}BC\bar{D}$ |

| AB | 11 | $AB\bar{C}\bar{D}$             | $AB\bar{C}D$             | $ABC\bar{D}$       | $ABC\bar{D}$       |

|    | 10 | $A\bar{B}\bar{C}\bar{D}$       | $A\bar{B}\bar{C}D$       | $A\bar{B}CD$       | $A\bar{B}C\bar{D}$ |

Simplification of Boolean expressions using Karnaugh Map

K-map accepts both SOP and POS versions, as is well known. Thus, the minterm and maxterm solutions are the two potential solutions for the K-map. Now let's get started by learning how to determine the K-map's minterm and maxterm solutions.

Karnaugh Maps (K-maps) provide a visual method for simplifying Boolean expressions. They help identify patterns and groups of 1s or 0s in the truth table, making it easier to minimize the expression.

### Steps to Simplify Boolean Expressions Using K-maps

- Create the K-map:** Draw a grid for the K-map corresponding to the number of variables in the expression.

- Fill the K-map:** Place the 1s and 0s in the K-map according to the truth table.

- Group the 1s (for SOP) or 0s (for POS):** Form groups of 1, 2, 4, 8, etc. Each group should be as large as possible.

- Write the simplified expression:** Write the Boolean expression for each group and combine them using OR (for SOP) or AND (for POS).

### Example: 3-Variable K-map Simplification

#### Truth Table

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

### Step 1: Create the K-map

For 3 variables (A, B, C), the K-map is a 2x4 grid:

|   |   | BC |    |    |    |   |

|---|---|----|----|----|----|---|

|   |   | 00 | 01 | 11 | 10 |   |

| A |   | 0  | 0  | 1  | 0  | 1 |

| 1 | 1 | 1  | 1  | 0  |    |   |

Step 2: Fill the K-map

|   |   | BC |    |    |    |   |

|---|---|----|----|----|----|---|

|   |   | 00 | 01 | 11 | 10 |   |

| A |   | 0  | 0  | 1  | 0  | 1 |

| 1 | 1 | 1  | 1  | 0  |    |   |

### Step 3: Group the 1s

Group the adjacent 1s in rectangles. Remember, groups must be powers of two (1, 2, 4, 8, etc.) and can wrap around edges.

|   |     | BC  |     |     |    |     |

|---|-----|-----|-----|-----|----|-----|

|   |     | 00  | 01  | 11  | 10 |     |

| A |     | 0   | 0   | (1) | 0  | (1) |

| 1 | (1) | (1) | (1) | 0   |    |     |

We can form the following groups:

- Group 1: (0,1), (1,1), (1,0), (0,0)

- Group 2: (1,1), (1,0)

### Step 4: Write the simplified expression

For Group 1:

- Variable B changes (0,1,0), so B is eliminated.

- Expression for Group 1: A

For Group 2:

- Variable A changes (0,1), so A is eliminated.

- Expression for Group 2:  $B \cdot \bar{C}$

Final simplified expression:

$$Y = A + B \cdot \bar{C}$$

#### 2.4.4 Don't Care Conditions

In some Boolean functions, certain input combinations never occur or the output doesn't matter. These are known as "don't care" conditions, represented by an 'X' in the truth table. Don't care conditions can be used in Karnaugh Maps (K-maps) to simplify expressions further by allowing flexibility in grouping 1s.

#### Example: Simplifying with Don't Care Conditions

#### Truth Table

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | X |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | X |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

#### Step 1: Create the K-map

For 3 variables (A, B, C), the K-map is a 2x4 grid:

|  |  | BC |   |    |   |    |   |    |  |

|--|--|----|---|----|---|----|---|----|--|

|  |  | 00 |   | 01 |   | 11 |   | 10 |  |

|  |  | A  | 0 | 1  | 1 | 0  | X |    |  |

|  |  | 1  | 1 | X  | 1 | 0  |   |    |  |

Step 2: Fill the K-map

|  |  | BC |   |    |   |    |   |    |  |

|--|--|----|---|----|---|----|---|----|--|

|  |  | 00 |   | 01 |   | 11 |   | 10 |  |

|  |  | A  | 0 | 1  | 1 | 0  | X |    |  |

|  |  | 1  | 1 | X  | 1 | 0  |   |    |  |

#### Step 3: Group the 1s and Xs

We can form groups using 1s and Xs to simplify the expression. Xs can be treated as either 0 or 1 to form the largest groups.

| BC          |     |     |     |

|-------------|-----|-----|-----|

| 00 01 11 10 |     |     |     |

| A           | 0   | 1   | (x) |

| 1           | (1) | (x) | (1) |

- Group 1: (0,0), (0,1), (1,0), (1,1)

- Group 2: (1,0), (1,1)

#### Step 4: Write the simplified expression

For Group 1:

- $A = 0$

- Variable C changes (0,1), so C is eliminated.

- Expression for Group 1:  $\bar{A}$

For Group 2:

- Variable A changes (0,1), so A is eliminated.

- Expression for Group 2:  $\bar{B} \cdot C$

Final simplified expression:

$$Y = \bar{A} + \bar{B} \cdot C$$

#### Essential Prime Implicants

Essential prime implicants are the groups in a K-map that cover at least one '1' that no other group covers. These are necessary for the simplified expression.

#### Example: Finding Essential Prime Implicants

#### Truth Table

| A | B | C | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

### Step 1: Create the K-map

For 3 variables (A, B, C), the K-map is a 2x4 grid:

|   |   | BC          |   |   |   |

|---|---|-------------|---|---|---|

|   |   | 00 01 11 10 |   |   |   |

| A | 0 | 1           | 1 | 0 | 1 |

|   | 1 | 0           | 0 | 0 | 1 |

Step 2: Fill the K-map

|   |   | BC          |   |   |   |

|---|---|-------------|---|---|---|

|   |   | 00 01 11 10 |   |   |   |

| A | 0 | 1           | 1 | 0 | 1 |

|   | 1 | 0           | 0 | 0 | 1 |

### Step 3: Group the 1s

We can form the following groups:

|   |   | BC          |     |   |     |

|---|---|-------------|-----|---|-----|

|   |   | 00 01 11 10 |     |   |     |

| A | 0 | (1)         | (1) | 0 | (1) |

|   | 1 | 0           | 0   | 0 | (1) |

### Step 4: Identify Essential Prime Implicants

- Group 1: (0,0), (0,1)  $\rightarrow \bar{A} \cdot \bar{B}$

- Group 2: (0,0), (1,1)  $\rightarrow \bar{C}$

- Group 3: (0,0), (0,1), (0,10)  $\rightarrow B \cdot \bar{A}$

Here, Group 1 and Group 2 are essential prime implicants because they cover unique 1s that no other group covers.

### Final Simplified Expression:

Combining the essential prime implicants, the final simplified expression is:

$$Y = \bar{A} \cdot \bar{B} + \bar{C} + B \cdot \bar{A}$$

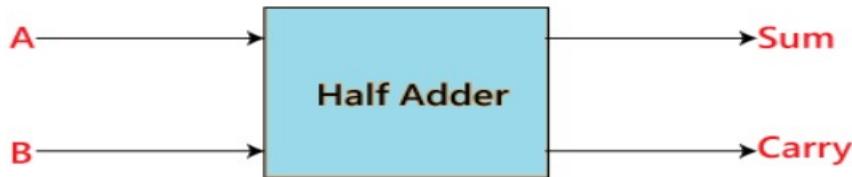

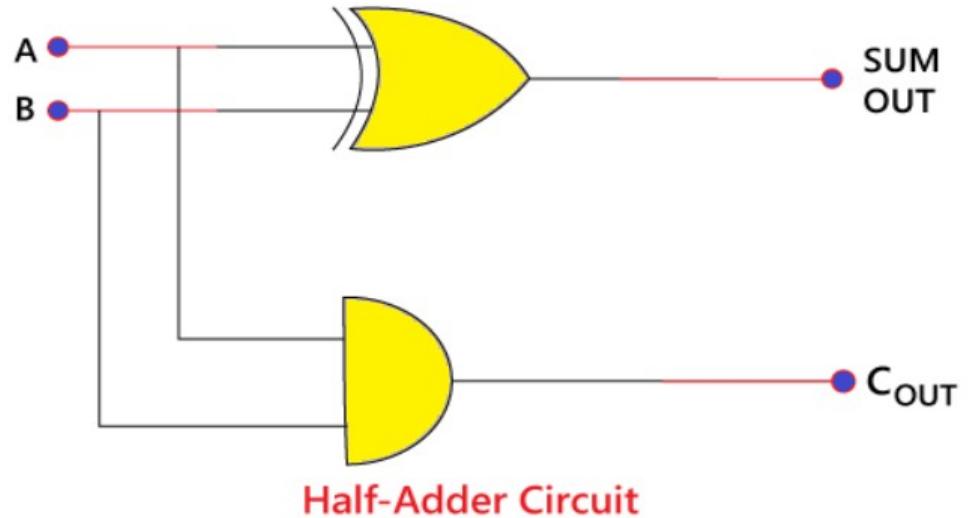

## 2.5 HALF ADDER

A fundamental building component for adding two numbers as inputs and producing two outputs is the half-adder. The OR operation of two single-bit binary values is carried out by the adder. The half adder has two output states, "carry" and "sum," and two input states, the augent and addent bits.

Block Diagram:

Truth table:

| Inputs |   | Outputs |       |

|--------|---|---------|-------|

| A      | B | Sum     | Carry |

| 0      | 0 | 0       | 0     |

| 0      | 1 | 1       | 0     |

| 1      | 0 | 1       | 0     |

| 1      | 1 | 0       | 1     |

In the table above,

- The input states are "A" and "B," while the output states are "sum" and "carry."

- When none of the inputs is 1, the carry output is 0.

- The 'sum' bit defines the least important part of the sum.

- The sum and carry have the following SOP form:

$$\text{Sum} = x'y + xy'$$

$$\text{Carry} = xy$$

### Design of Half Adder Circuit:

As can be seen, the block diagram has two inputs and two outputs.